Verarbeitung von Multimedia-Informationen mit einer neuen Prozessorgeneration für mobile Geräte

Mobile Media Processing der Zukunft

Fortsetzung des Artikels von Teil 1

Mobile Media Processing der Zukunft

Effizientes Computing

Die VLES-Software-Architektur (Variable Length Execution Set) ist eine Implementierung der VLIW-Architektur mit besonders geringem Leistungsverbrauch und hoher Code-Dichte. Anstatt Befehlssätze mit festen Längen zu verwenden, benutzt die VLES-Architektur eine 16-bit-Instruction-Set-Architecture und Präfixe, um dieselbe Leistungsfähigkeit zu erreichen, die normalerweise den Befehlen mit fester Wortlänge eigen ist. Parallelverarbeitung wird dadurch erzielt, dass bis zu sechs Befehle zu einem Befehlssatz zusammengefügt werden können, der in den meisten Fällen in einem einzigen Zyklus abgearbeitet werden kann. Die komplexe Hardware, die das Pipeline-Interlocking und Scheduling fordern, ist teilweise an Programmier-Tools ausgelagert, um die Kosten und den Leistungsverbrauch zu reduzieren. Verknüpfte Takte (gated clocks) sind über den gesamten Prozessorkern verteilt, was den Leistungsverbrauch senkt, wenn die Verarbeitungseinheiten nicht benutzt werden.

Die Erweiterung um applikationsspezifische Befehle steigert die Leistungsfähigkeit der Video- und Audio-Bearbeitung noch weiter. Drei verschiedene Kategorien von Befehlen wurden hinzugefügt:

- zusätzliche Shift- und Bit-Reverse-Befehle für die Audio-Bearbeitung,

- parallele Byte-Move-Operation-Befehle für den Transport von Video-Daten,

- SIMD2-Befehle, um DSP-intensive Video-Datenverarbeitungs-Kernel zu beschleunigen.

Die ISA-Erweiterungen beschleunigen DSP-intensive Algorithmen für Audio- und Video-Codecs wesentlich. Für Audio ist diese Kernel-Beschleunigung wichtig zur Steigerung der Gesamtleistung des Codecs. Zwei Beschleunigungsarten sind für Video-Codecs nötig: die der Kernel-Befehle und die der Steuerbefehle. Das Verfahren zur Beschleunigung des Steuercodes ist im nächsten Absatz beschrieben.

Statt jeden applikationsspezifischen Befehl aufzulisten, wird der SAD4-Befehl als Beispiel für die Arbeitsweise der Architektur gewählt. Dieser Befehl führt vier Byte-Substraktionen durch und addiert dann die absoluten Werte der Ergebnisse und sendet sie an das gewünschte Zielregister – alles in einem einzigen Zyklus. Der detaillierte Ablauf dieses SIMD2-ähnlichen Befehls kann wie folgt dargestellt werden:

Dn.L+|Dh.HH - Dg.HH|+

+|Dh.HL - Dg.HL|+|Dh.LH-Dg.LH|+

+|Dh.LL-Dg.LL|→Dn.L

Dn, Dh und Dg bezeichnen die Quell- und Zielregister, HH, HL, LH sowie LL die Bytes eines 32-bit-Registers. Der SAD4-Befehl kann zur Bewegungsbestimmung bei der Video-Codierung verwendet werden und erreicht eine um maximal 13-fach beschleunigte Verarbeitung der Daten im Vergleich zum SC1400-Core.

Jobangebote+ passend zum Thema

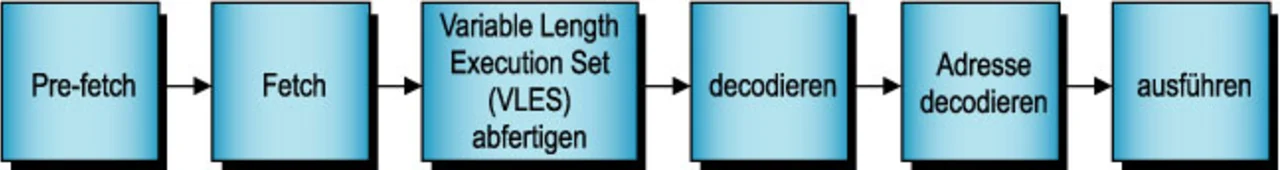

Die Architektur der SC2000-Familie beinhaltet eine sechsstufige Pipeline, wie in Bild 4 dargestellt. Die dynamische Branch Target Prediction und die Stack-Pointer-Vorausberechnung wurden eingeführt, um die Leistung des zur Steuerung benötigten Teils des Code zu steigern. Interne Untersuchungen von StarCore belegen, dass etwa 30 bis 40 % der Zyklen eines MPEG-4-Encoders für die steuerungsähnlichen Teile des Codec verwendet werden, was eine Vielzahl an zu durchlaufenden Schleifen bedeutet. Es wurde eine Zunahme solcher Code-Teile um circa 20 % beobachtet.

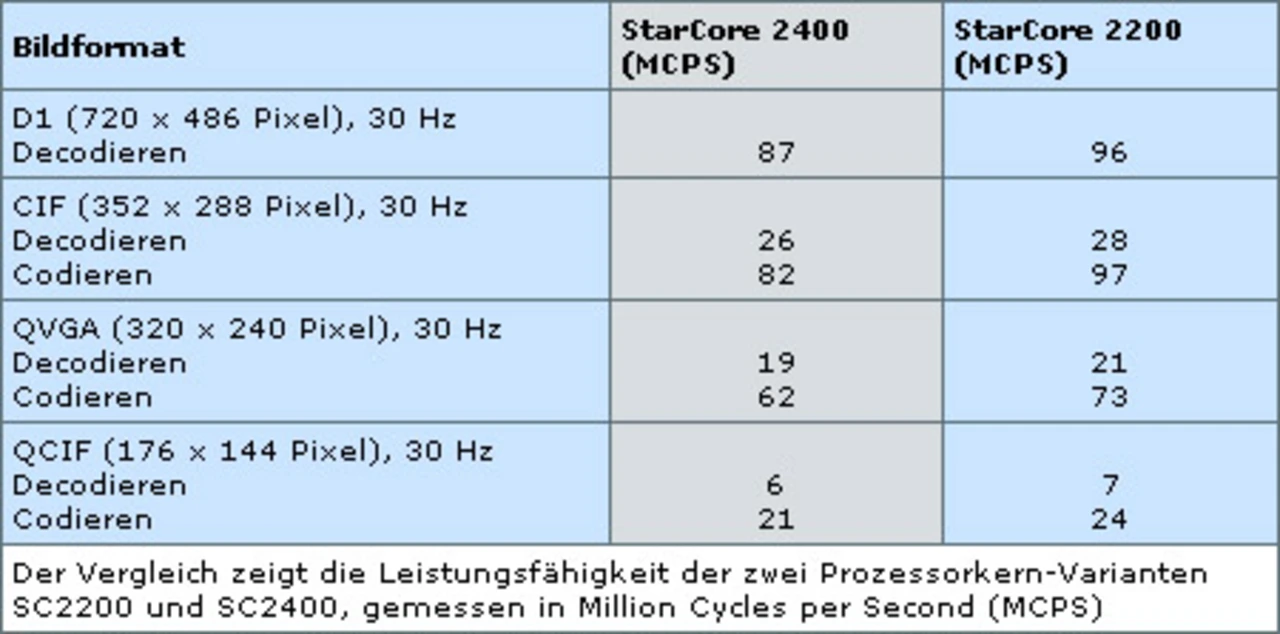

Basierend auf ähnlichen Implementierungen auf dem SC1400-Kern wurde die beschleunigte Bearbeitung für MPEG-4-Video-Encoder und -Decoder analysiert. Die zusätzliche Beschleunigung des Kernels und des Steuer-Code wurde ebenfalls betrachtet. Die MCPS-Werte (Million Cycles per Second) in der Tabelle zeigen die geschätzte, schlechteste Ein-Sekunden-DSP-Durchschnittslast für die Implementierung eines CIF-Decoders/Encoders bei 30 Bildern/s und 512 Kbit/s Übertragungsrate. Mit der bewegungsreichen Videosequenz „Foreman“ – bestehend aus 400 Bildern im QCIF-Format (144 x 176 Bildpunkte) – sind diese statistischen Vergleichswerte ermittelt worden. Für den Decoder ist ein direkter Speicherzugriff (DMA, Direct Memory Access) verfügbar, um die decodierten Videosignale an den Display-Buffer zu senden und den Referenz-Frame in den und aus dem Decoder-Bildspeicher zu kopieren. Für den Encoder werden proprietäre Algorithmen für die Bewegungssuche (motion search), Auswahl der Modi und Steuerung der Übertragungsrate eingesetzt. DMA ist verfügbar zum Senden von rohen Video-Daten, zum Codieren und Zugreifen auf Referenz-Frame(s) sowie zum Senden von codierten Bitströmen in den Speicher. Sowohl für den Codierer als auch den Decodierer werden alle Programm- und anderen Datenzugriffe über ein internes SRAM ohne Wait-States ausgeführt. Für die DMA-Konfiguration wird kein Overhead vorausgesetzt.

- Mobile Media Processing der Zukunft

- Mobile Media Processing der Zukunft

- Mobile Media Processing der Zukunft