6-Gbit/s-Bausteine auf dem Prüfstand

Herausforderung: Test von „High-Speed ICs“

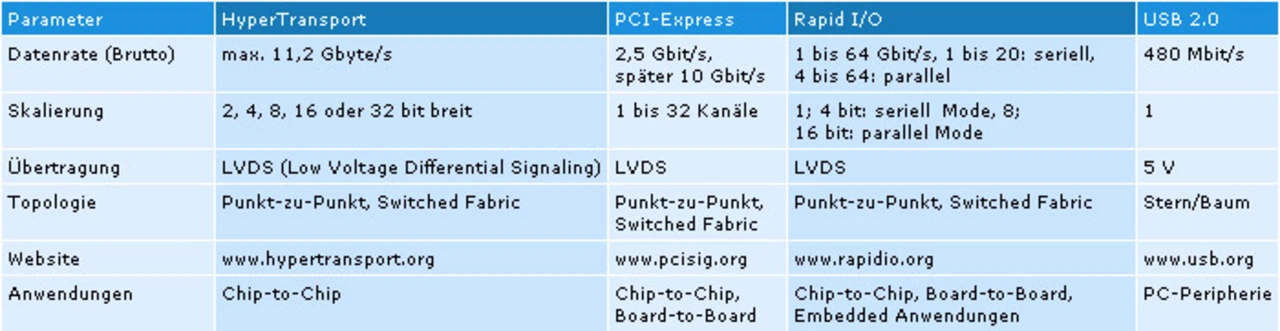

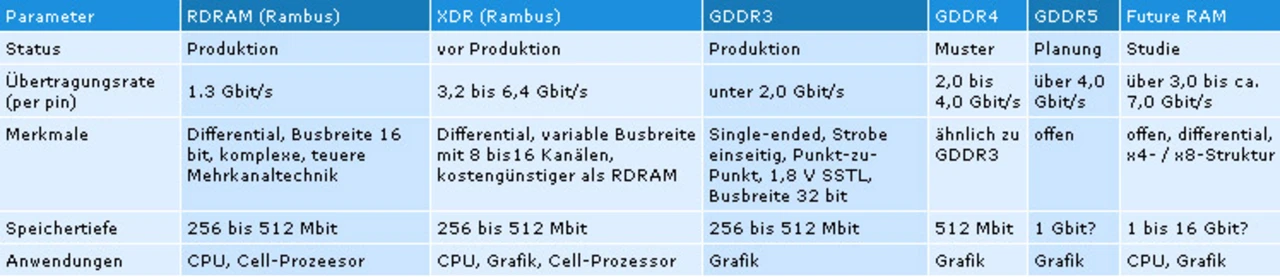

Waren extrem hohe „Per-pin-Datenraten“ bisher vorwiegend bei schnellen seriellen Schnittstellen wie zum Beispiel PCI-Express, Rapid I/O oder Serial ATA anzutreffen, so stoßen kommende DRAM-Generationen wie GDDR3/4 oder XDR in den Bereich 2 Gbit/s und darüber vor, wobei auch hier „kein Ende der Fahnenstange“ ersichtlich ist. Bauteile mit derartig hohen Übertragungsraten mit der nötigen Testabdeckung zu prüfen, stellt extrem hohe Anforderungen an die Testsysteme.

6-Gbit/s-Bausteine auf dem Prüfstand

Waren extrem hohe „Per-pin-Datenraten“ bisher vorwiegend bei schnellen seriellen Schnittstellen wie zum Beispiel PCI-Express, Rapid I/O oder Serial ATA anzutreffen, so stoßen kommende DRAM-Generationen wie GDDR3/4 oder XDR in den Bereich 2 Gbit/s und darüber vor, wobei auch hier „kein Ende der Fahnenstange“ ersichtlich ist. Bauteile mit derartig hohen Übertragungsraten mit der nötigen Testabdeckung zu prüfen, stellt extrem hohe Anforderungen an die Testsysteme.

Jobangebote+ passend zum Thema

Die Schwierigkeiten beim Test von ICs mit hohen Datenübertragungsraten liegen – auf einen Nenner gebracht – im geringen Spannungshub und in der teilweise asynchronen Funktion der Bauteile gegenüber dem synchronen Verhalten eines Testsystems. Zur Vereinfachung des Tests werden daher auch bauteilinterne Scan- oder BiST-Funktionen (Boundary Scan, Built-in Self Test) oder das Loop-back-Verfahren genutzt (Schleifentest von Übertragungskanälen: Dabei wird vom zu prüfenden Element ein Testmuster ab- und von einem Empfänger im Testsystem wieder zurückgeschickt; das zurückgesendete Testmuster wird anschließend mit dem Originalmuster verglichen). Für einen umfassenden At-Speed-Test wird jedoch ein geeignetes High-Speed-Modul benötigt, das einerseits kostengünstig sein muss und mit dem sich andererseits im Produktionstest-Betrieb ein hoher Durchsatz erreichen lässt.

At-Speed-Test mit einem neuen High-Speed-Digital-Modul

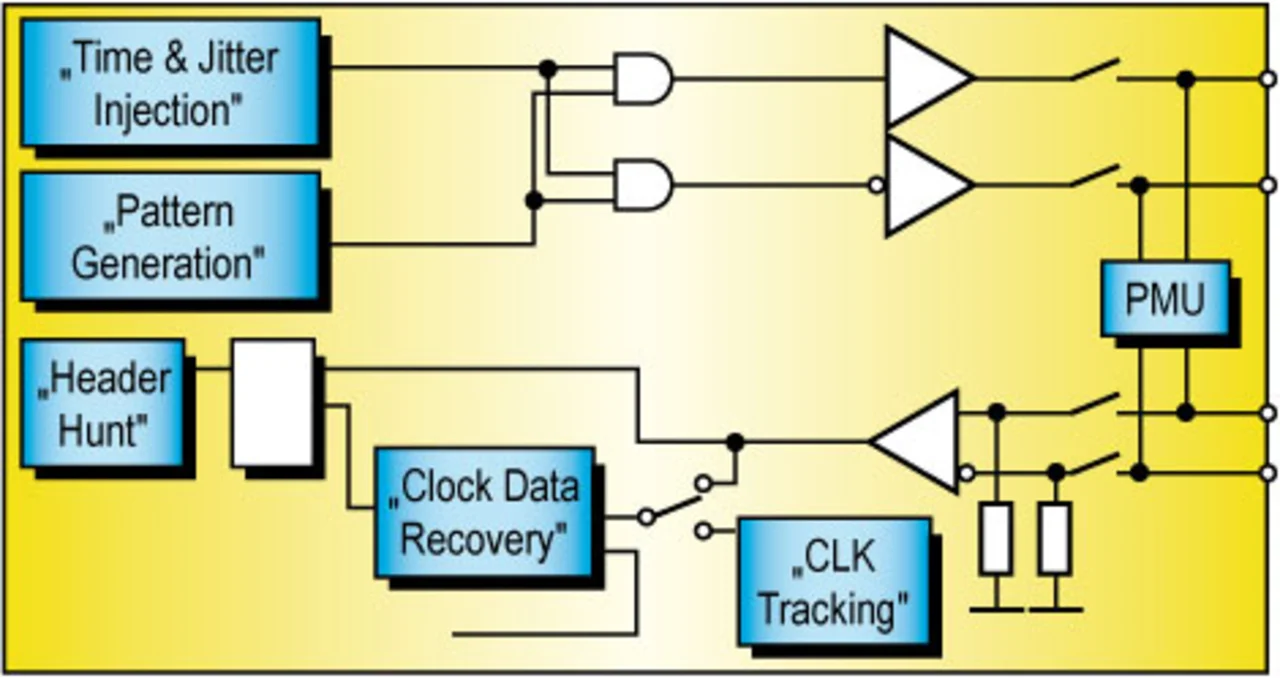

Mit dem „6.5G-Digital-Modul“ für die Testplattform T2000 von Advantest (www.advantest.de) lassen sich nun serielle Schnittstellen (Übersicht in Tabelle 1) sowie zukünftig auch schnelle DRAMs (Übersicht in Tabelle 2) sozusagen „at speed“ testen. Hierfür ist das Modul mit 32 Leitungen für die acht differentiellen Ein- und Ausgänge ausgerüstet. Folgende Schlüsselfunktionen dieses Moduls sind in der Prinzipschaltung in Bild 1 dargestellt:

- Header Hunt: Zur Kompensation von nicht-deterministischen Unterbrechungen zwischen gesendeten Datenpaketen.

- Taktverfolgung ( CLK Tracking): Zur Unterstützung von quellensynchronen Systemen bei seriellen Schnittstellen und DRAMs.

- Taktregenerierung (Clock Data Recovery): Zur Datenssynchronisation mit Hilfe eines integrierten Taktes.

- Time&Jitter-Injection-Fähigkeit: Bei jedem Treiber-Kanal kann während der Patternausführung ein anpassbares, sinusförmiges Jittersignal zu- oder abgeschaltet werden.

- Pattern- (Prüfmuster-) Generator mit 32 MWorten je Kanal Speichertiefe und der Möglichkeit zur Per-pin-Pattern-Kompression bei großen Pattern.

- PMU per Pin für Spannungspegel von –1 bis +3,3 V.

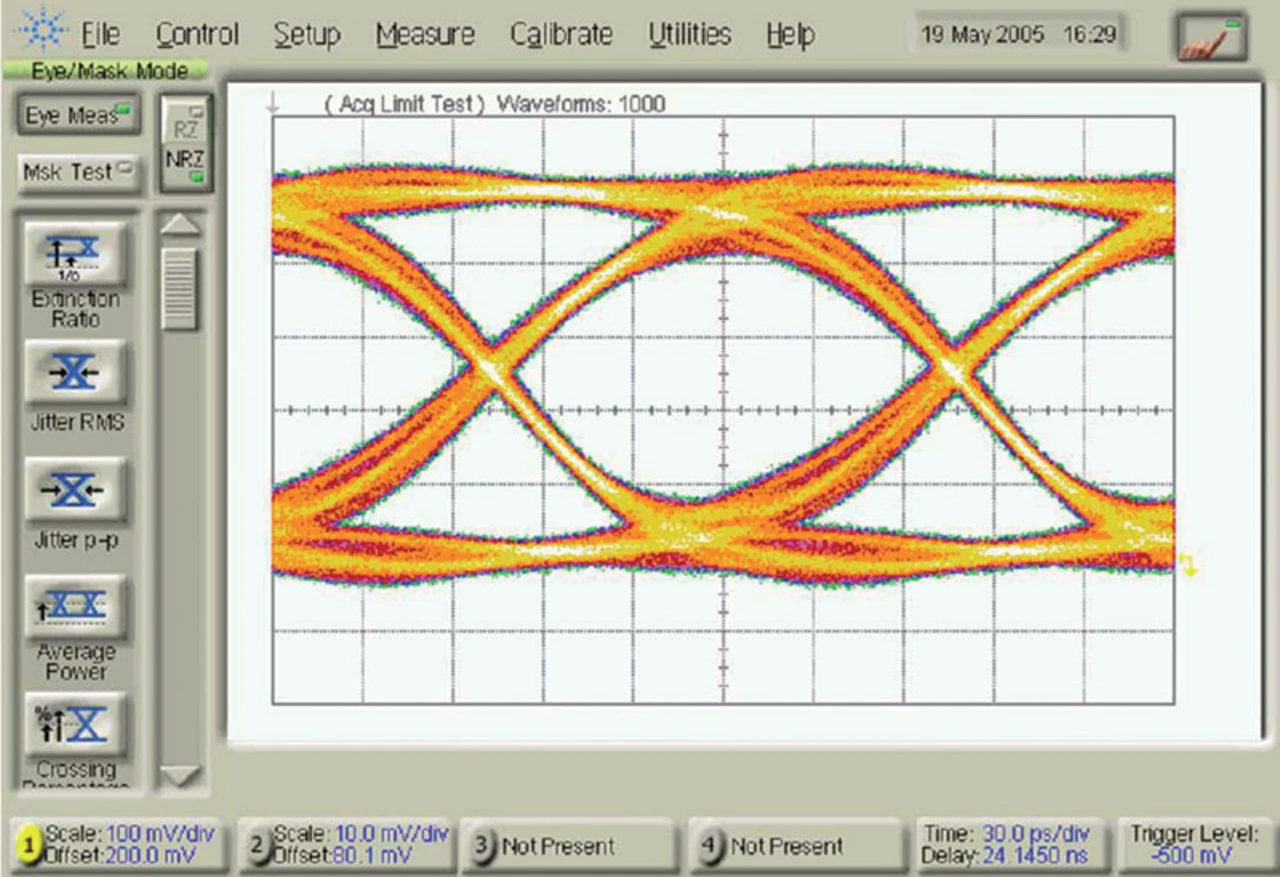

Zur Verdeutlichung der technischen Fähigkeiten des Moduls wird das Augendiagramm eines 5,0-Gbit/s-SerDes-Bauteils (Serializer/Deserializer) gezeigt (Bild 2). Die Messung wurde mit dem neuen 6.5G-Modul in einem T2000-System (Aufmacherbild) durchgeführt und unter Nutzung der Pre-Emphasis-Funktion des Moduls erzeugt. Damit kann der Strom am Treiber-Ausgang erhöht werden, wodurch die Toleranzen beim Zeit- und Spannungsverlauf speziell bei sehr geringem Spannungshub erhalten bleiben, was die Signalqualität des „Daten-Auges“ verbessert.

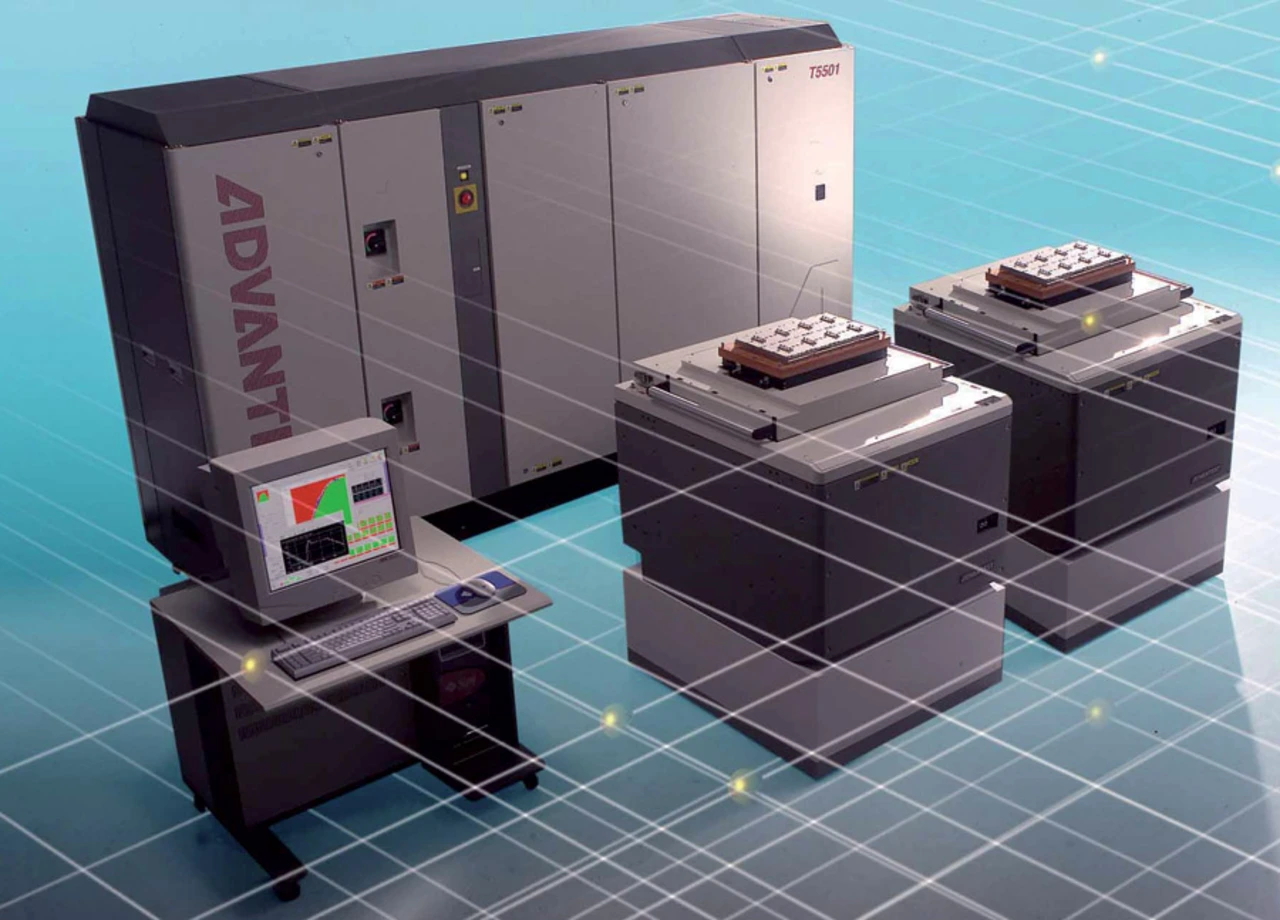

Letztlich wurde das 6.5G-Modul zum vektorbasierten Testen schneller quellensynchroner und SerDes-Schnittstellen entwickelt. Eine Anwendung des Moduls im SoC-Tester T2000 für zukünftige Hochgeschwindigkeits-DRAMs speziell ab 4 Gbit/s ist mit einigen Anpassungen am Modul ebenfalls denkbar. Für einen wirtschaftlichen Produktionstest dynamischer Speicher bis 4 Gbit/s ist allerdings der GHz-DRAM-Tester T5501 (Bild 3) besser eingesetzt. Hierzu wird das System mit einem High-Speed-Takt und einer Spezialfunktion ausgerüstet, die ein Auslesen von vier Datenraten innerhalb eines Zyklus erlaubt.

- Herausforderung: Test von „High-Speed ICs“

- Autor