Leiterplattendesign

Für das Testen entwickeln

Fortsetzung des Artikels von Teil 2

JTAG/Boundary Scan – Grundlegendes und Möglichkeiten

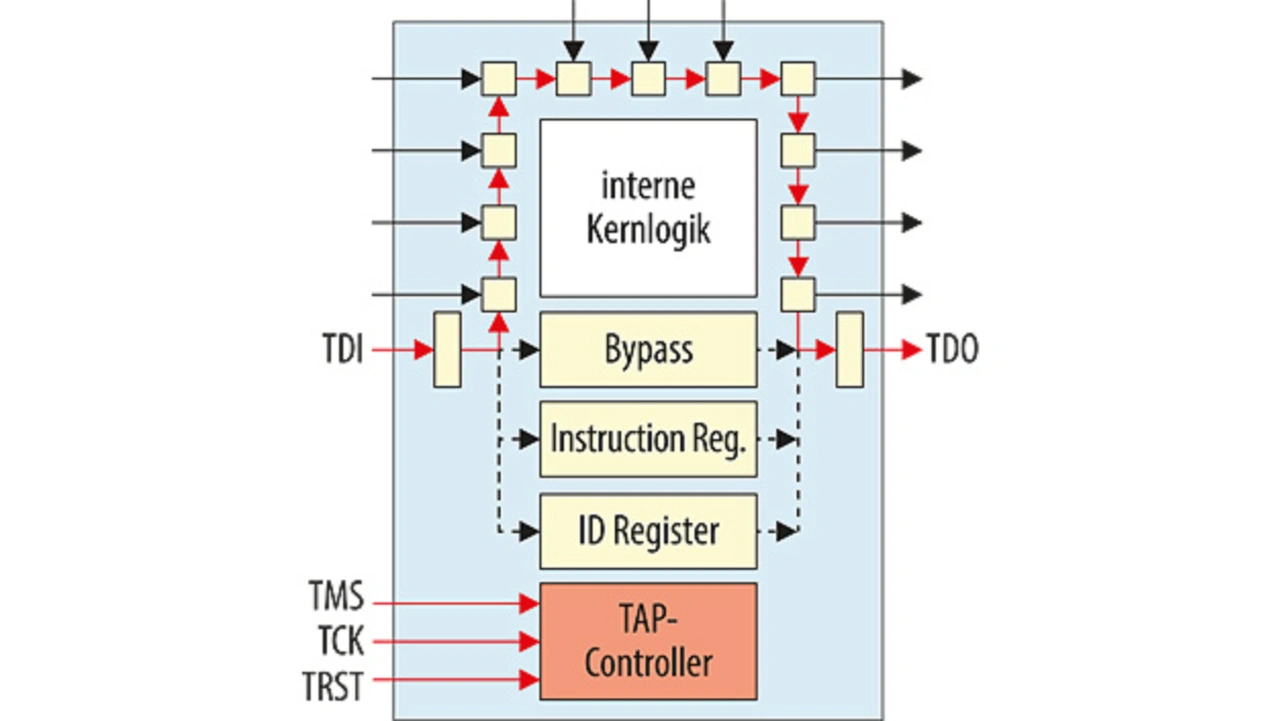

Bauteile mit Boundary Scan erhalten zusätzlich zur normalen Funktion ein Schieberegister, das mit den I/O-Pins verbunden ist und die Bauteilgrenze (Boundary) darstellt. Jedem (digitalen) Pin des Bauteils sind eine oder mehrere Zellen dieses Schieberegisters zugeordnet (Bild a). Über diese Zellen lassen sich die Bauteilpins steuern bzw. messen, unabhängig von der eigentlichen Funktionalität, der Kern-Logik des Bauteils.

Die Verbindung zwischen den Pins von zwei oder mehr Boundary-Scan-Bauteilen lässt sich sehr leicht verifizieren. Es genügt, über das Boundary-Scan-Register eine 0 oder 1 am Ausgangspin auszugeben und den Wert an den Eingangspins der verbundenen Boundary-Scan-Bauteile über deren Boundary-Scan-Register einzulesen. Das ist die grundlegende Arbeitsweise von Boundary Scan.

So können die Verbindungen zwischen Boundary-Scan-Bauteilen ganz einfach verifiziert werden, selbst wenn nicht-Boundary-Scan-Bauteile dazwischengeschaltet sind. Ein simples Beispiel für ein derartiges Bauteil ist ein Serienwiderstand.

Wenn Boundary-Scan-Bauteile mit den Adress-, Daten- und Steuerleitungen eines Flash-Speichers verbunden sind, kann der Speicher über die Boundary-Scan-Register dieser Bauteile beschrieben und ausgelesen werden. Auf diese Art lassen sich Flash-Speicher direkt in der Schaltung (In-System) durch JTAG programmieren.

Jobangebote+ passend zum Thema

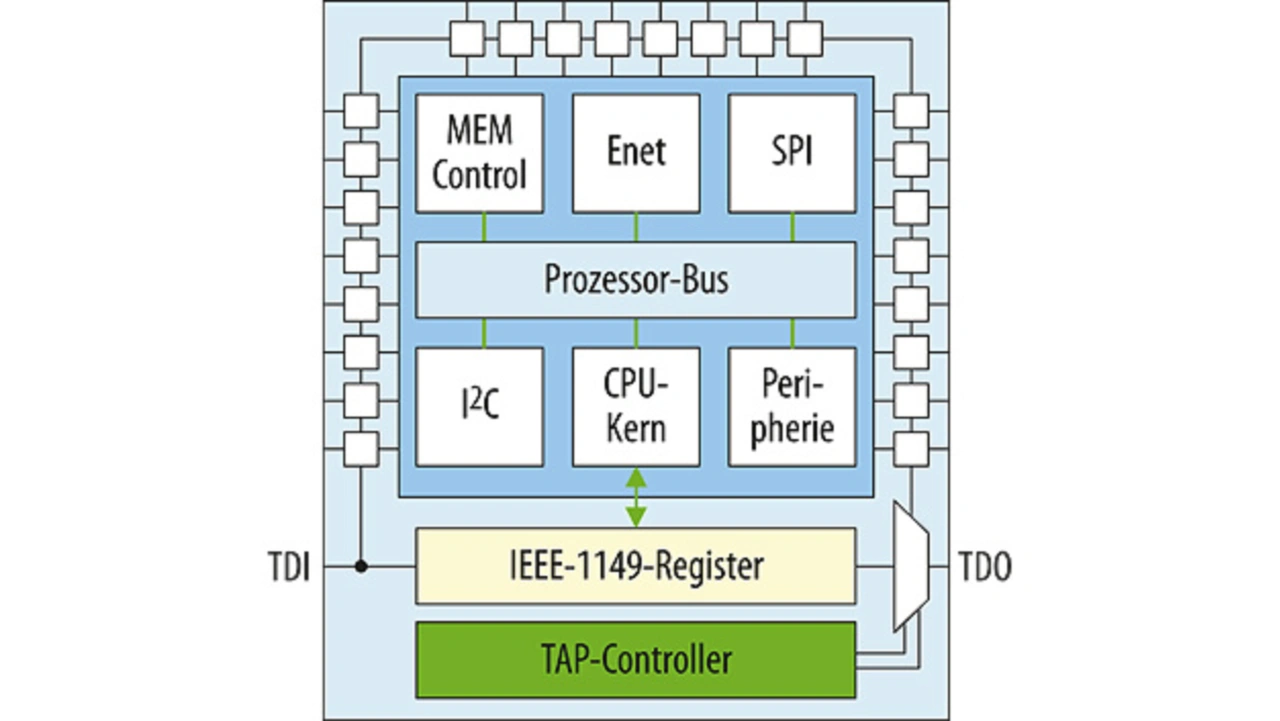

Mikroprozessoren enthalten häufig eine spezielle, über JTAG erreichbare Debug-Logik zur Unterstützung des Software Debugging (Bild b). Diese Logik kann sich in Ergänzung des Boundary-Scan-Registers auf dem Chip befinden. Manchmal ist jedoch gar kein Boundary-Scan-Register im Chip enthalten. Über die Debug-Logik lässt sich die vollständige JTAG-Kontrolle des CPU-Kerns, seiner Busse und aller verbundenen Strukturen realisieren. Die Debug-Logik lässt sich also nutzen, um Tests und In-System-Programmierungen durchzuführen (emulative(r) Test & Programmierung). Die Schnittstellen von JTAG Technologies‘ CoreCommander kommunizieren direkt mit der Debug-Logik eines Mikroprozessors und bieten volle Kontrolle über den Prozessorkern. Die Ausführungen des CoreCommander sind spezifisch für einen Prozessorkern, einen Prozessortyp oder eine ganze Prozessorfamilie. Die Funktionen von CoreCommander – seine API – sind vollständig unabhängig vom Typ des Prozessorkerns.

- Für das Testen entwickeln

- Überprüfung von Testbarkeit und Fehlerabdeckung

- JTAG/Boundary Scan – Grundlegendes und Möglichkeiten