Boundary-Scan-Test

Baugruppen auf dem Prüfstand

Auch eine optimal eingerichtete Fertigungslinie für elektronische Baugruppen wird nie einhundertprozentig perfekte Qualität liefern, dazu gibt es zu viele Fehlerquellen. Unter bestimmten Bedingungen kann das Testverfahren JTAG/Boundary Scan dabei helfen, Probleme früh im Produktionsprozess zu finden.

Dass die bleifreie Fertigung deutlich geringere Prozesstoleranzen erfordert als herkömmliche Methoden, führt immer noch zu Schwierigkeiten. Hinzu kommt die Tatsache, dass viellagige Leiterkarten, Blind- und Buried-Vias, kleine und dichte Pads, Bauteile mit hunderten von Pins und auch BGA-Gehäuse das Fehlerrisiko erhöhen und es erschweren, manche Fehler zu erkennen. Doch Fehler treten nun mal auf, und je später im Produktionsprozess sie gefunden werden, desto ärgerlicher und teurer wird es.

Dazu kommt, dass von Funktionstests gemeldete Fehler häufig schwer zu lokalisieren sind; gerade bei komplexeren Designs gibt es viele mögliche Ursachen, warum eine bestimmte Funktion versagt. Und wenn mehrere Fehler zusammenkommen, ist die Diagnose noch schwieriger. Wenn dann nach mehreren Stunden Fehlersuche die Baugruppe noch immer nicht funktioniert, muss die immer ärgerliche Entscheidung getroffen werden, die Herstellungskosten und die schon investierte Zeit abzuschreiben.

Jobangebote+ passend zum Thema

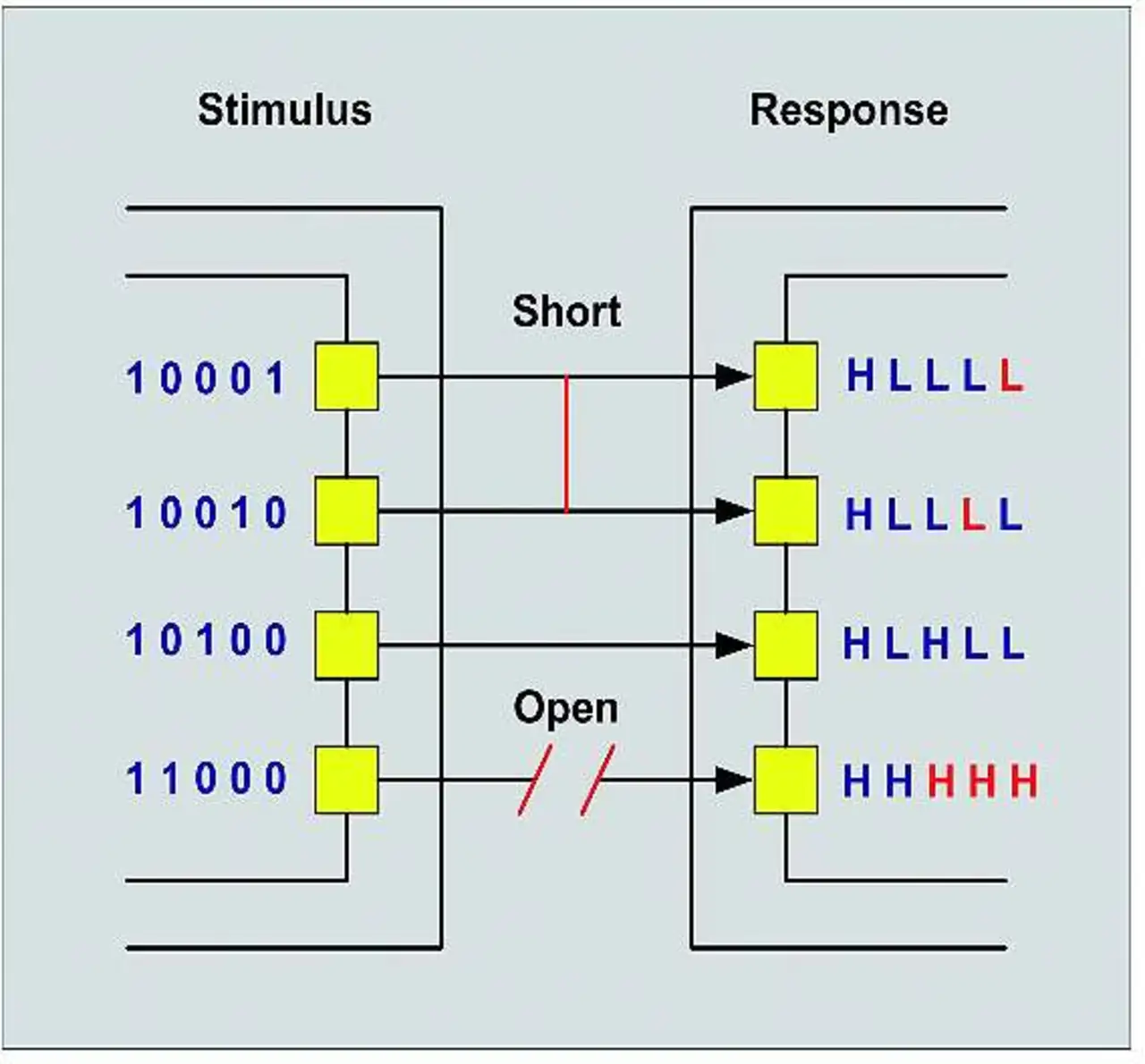

Eine sinnvolle Ergänzung zu herkömmlichen Testverfahren bietet JTAG/Boundary Scan: Viele komplexe digitale Bausteine lassen sich in einen Boundary-Scan-Testmodus schalten, in dem über eine spezielle serielle JTAG-Schnittstelle die Ausgangspegel aller Anschlüsse gesteuert und die Eingangspegel ausgelesen werden können. Nach außen braucht von der Leiterkarte nur eine einzige JTAG-Schnittstelle mit vier Signalen herausgeführt werden, da die Boundary-Scan-Bausteine auf der Karte im JTAG-Pfad hintereinandergeschaltet werden können. Boundary-Scan-fähige Bausteine können sich gegenseitig testen und erwartete Pegel auf Leitungen überprüfen. Ebenso können an solche Bauteile angeschlossene Signale mit bekannten Pegeln getestet werden. So lassen sich typische Produktionsfehler wie offene Lötstellen und Kurzschlüsse direkt finden (Bild 1).

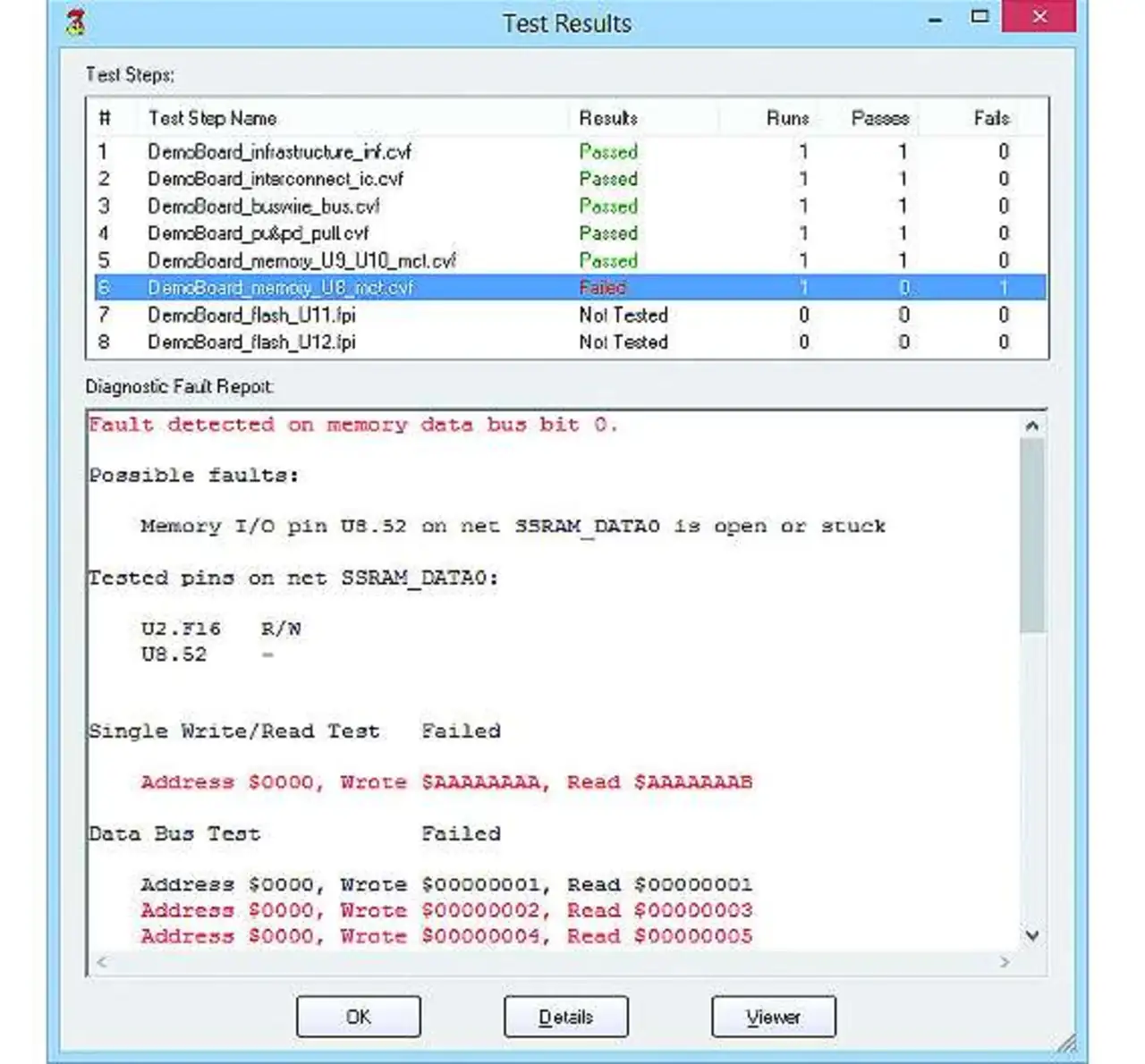

Moderne Software wie der »ScanExpress Runner mit Advanced Diagnostics« (Bild 2) von Corelis erkennt anhand der eingelesenen Eingangspegel den Fehlertyp wie auch die vermutlichen Fehlerursachen und -orte auf der Leiterkarte und gibt diese genau an.

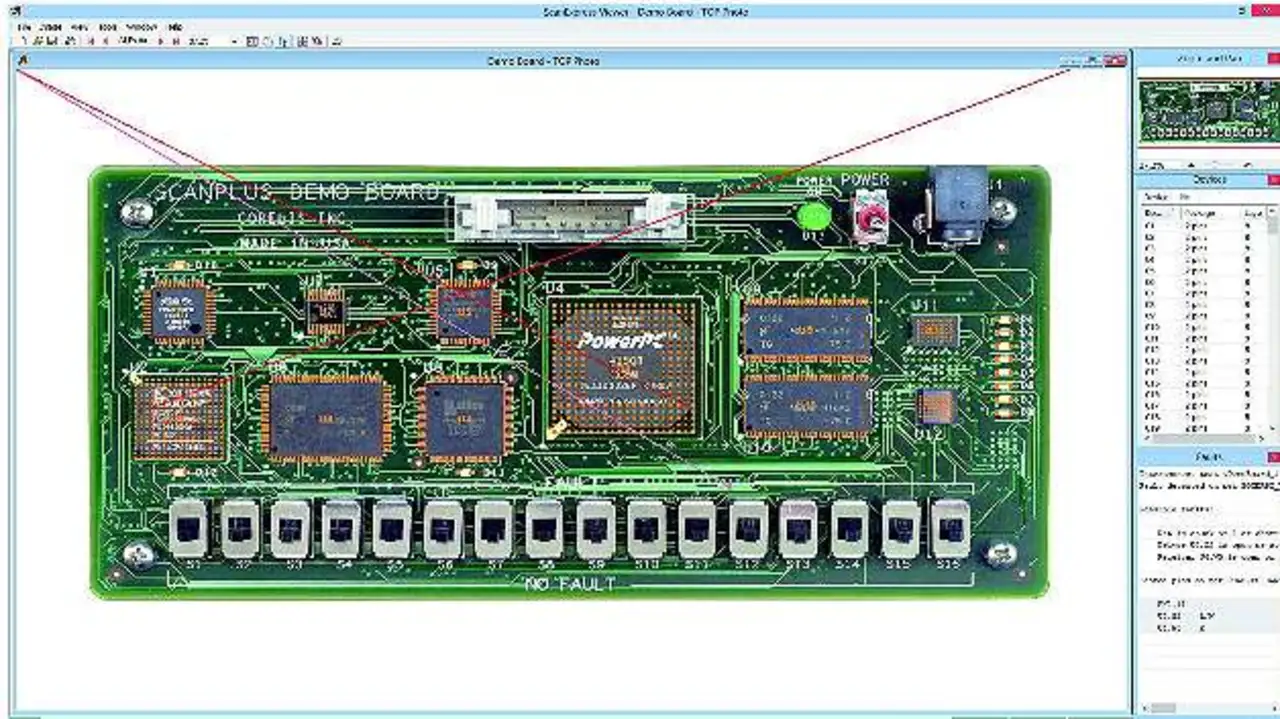

Für den Reparaturtechniker kann auch noch die Lage der vermutlich betroffenen Pins auf der Leiterkarte grafisch angezeigt werden (Bild 3). Selbst an ein Boundary-Scan-fähiges Bauteil angeschlossene flüchtige wie nichtflüchtige Speicher lassen sich testen, Letztere sind ebenso wie CPLDs auch programmierbar. Damit können im Produktionsablauf nötige Bauteileprogrammierungen im Rahmen eines Boundary-Scan-Tests gleich mit erledigt werden.

Vergleich mit anderen Testverfahren

Vor einem Boundary-Scan-Test empfiehlt sich eine AOI (optische Inspektion) um sicherzustellen, dass beispielsweise Widerstände oder Kondensatoren mit den richtigen Werten eingesetzt wurden. Boundary Scan eignet sich gut für Baugruppen mit hohem Digitalanteil, weniger gut für Schaltungen mit vielen Analogbauteilen. Bereits bei der Schaltungsentwicklung ist die Testmethode zu berücksichtigen; es müssen Boundary-Scan-fähige Bauteile zum Einsatz kommen, die in den JTAG-Schnittstellenpfad eingebunden werden. Seine Stärke entfaltet dieser Test besonders bei komplexen und sehr dichten Baugruppen sowie bei Baugruppen mit Bauteilen im BGA-Gehäuse:

- Bei komplexen Baugruppen können Funktionstests selten mit genügender Testtiefe testen, es werden Fehler übersehen. Und wenn ein Funktionstest einen Fehler meldet, ist er häufig schwer einzugrenzen. Boundary-Scan dagegen findet in den testbaren Schaltungsteilen die meisten Lötfehler und kann diese zudem genau lokalisieren, sodass sie sich einfacher reparieren lassen. Da¬rüber hinaus sind In-Circuit-Tester (ICTs) für sehr komplexe Baugruppen groß, schwer und sehr teuer.

- Sehr dichte Baugruppen haben häufig keinen Platz, um alle Testpunkte für einen In-Circuit-Tester herauszuführen. Boundary-Scan benötigt nur eine einzige herausgeführte JTAG-Schnittstelle.

- Die Lötverbindungen von BGA-Gehäusen lassen sich nicht optisch überprüfen, sondern nur durch aufwendiges Röntgen. Ebenso ist es kaum möglich, alle Kontakte auf Testpunkte für einen In-Circuit-Tester herauszuführen. Die meisten BGA-Bauteile sind heute bereits Boundary-Scan-fähig und lassen sich so leicht auf Lötfehler testen.

Auch bei Baugruppen, die nicht komplett mit Boundary Scan testbar sind, ist häufig eine Kombination aus Boundary Scan und ICT sinnvoll: Der ICT-Aufwand wird minimiert, es müssen weniger Testpunkte herausgeführt werden, und es lassen sich auch mit dem ICT schwer oder gar nicht erreichbare Anschlüsse testen.

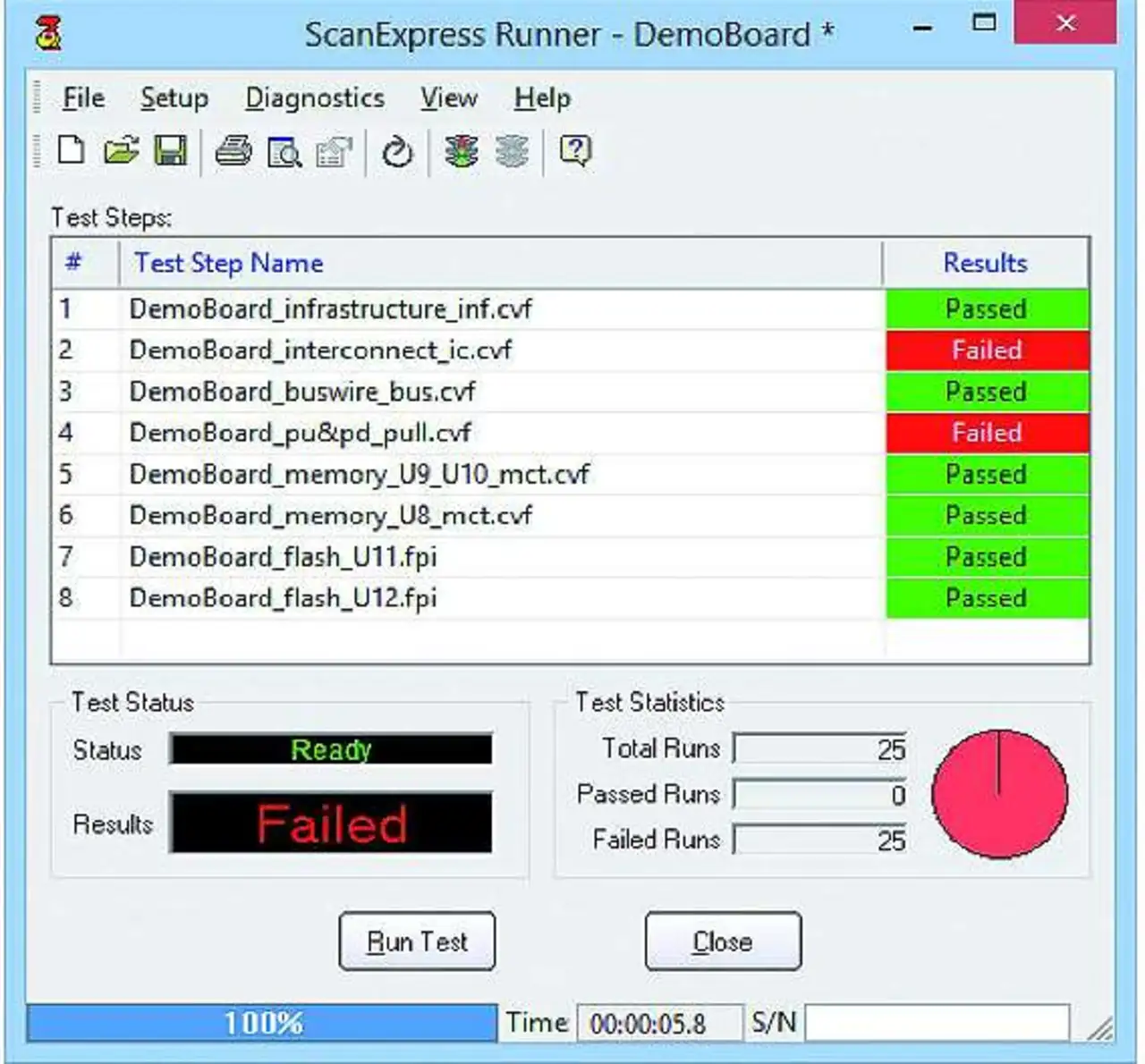

Für viele ICTs und Flying Probes existiert bereits eine fertige Unterstützung (beispielsweise bei Agilent, Checksum, Teradyne, Scorpion, Spea, Digital Test, Seica), andere können über DLLs integriert werden. Im Vergleich zu anderen Testverfahren hat Boundary Scan einen überschaubaren Aufwand – wenn die zu testende Baugruppe passend entwickelt wurde: Man benötigt nur eine herausgeführte JTAG-Schnittstelle, einen JTAG-Controller zur Verbindung mit dem PC (Bild 4), den PC mit der entsprechenden Software und einen für die zu testende Baugruppe entwickelten Testplan. Typischerweise zeigt die Software die einzelnen Testschritte nebst Erfolg oder Misserfolg an (Bild 5). Gefundene Fehler werden protokolliert, sodass deren Beseitigung auch später und an einem anderen Arbeitsplatz stattfinden kann. Statistische Auswertungen unterstützen das Qualitätsmanagement des Anwenders.

Testpläne erstellen

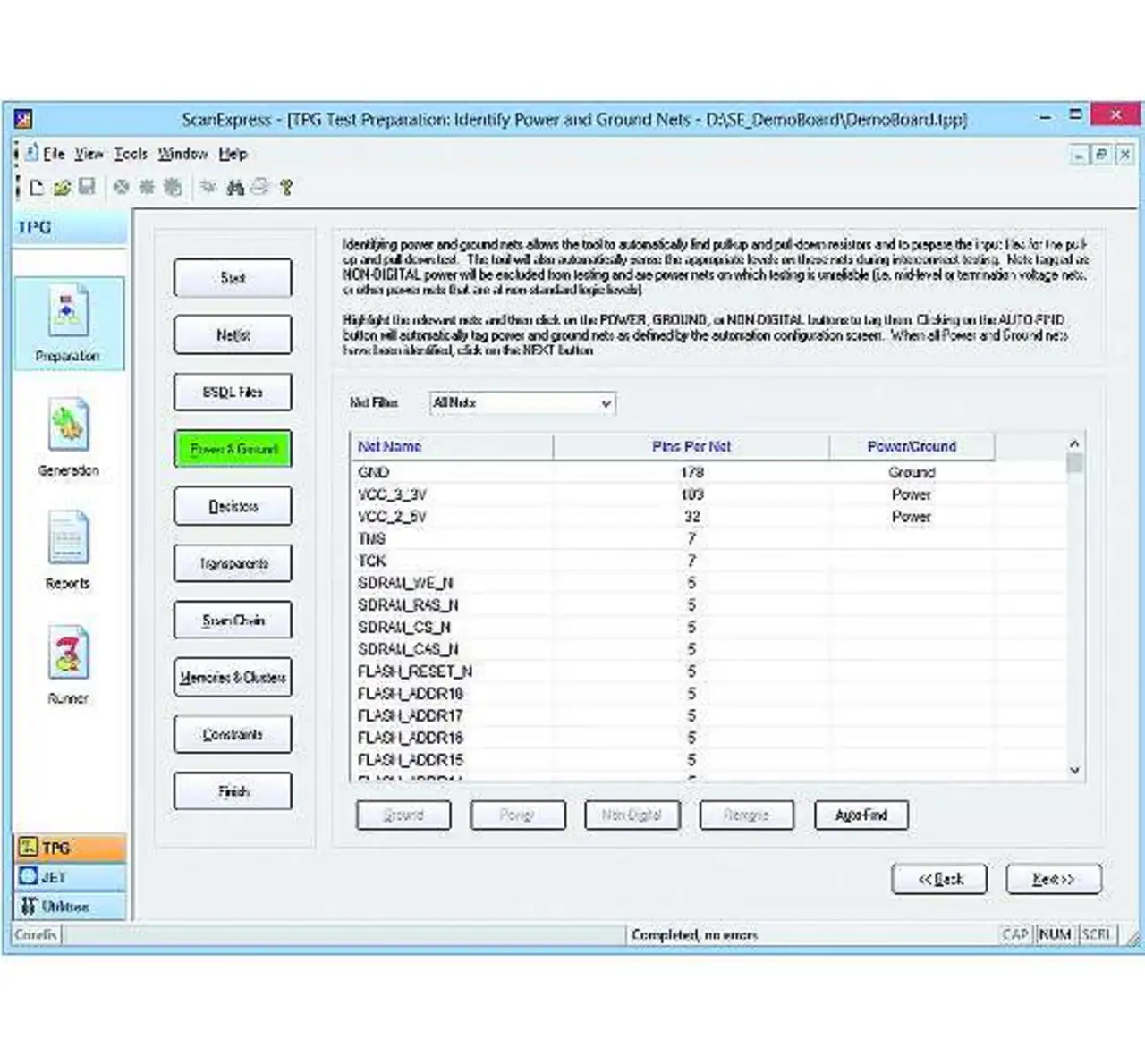

Die Erstellung des Testplans ist noch die schwierigste Aufgabe bei einem Boundary-Scan-Test. Der »ScanExpress Test Plan Generator« (Bild 6) von Corelis führt mit einem Wizard durch alle Schritte bis zum fertigen Testplan. Zuerst liest das Tool Netzliste, Schaltplan und Bauteileliste (BOM) ein, wobei die allermeisten Netzlistenformate unterstützt werden. Im zweiten Schritt werden die BSDL-Dateien der Boundary-Scan-fähigen Bauteile eingelesen. Danach findet die Identifizierung von Versorgungsspannungs- und Massenetzen statt, anschließend die der Widerstände (Pull-ups, Pull-downs und Serienwiderstände). Bei all diesen Schritten erkennt das Werkzeug die Funktion der meisten Bauteile automatisch, es sind nur geringe Nacharbeiten erforderlich. Zuletzt werden Speicherbausteine identifiziert. Das Werkzeug kennt die meisten gängigen Speichertypen; neue Speichertypen werden regelmäßig hinzugefügt, und falls einmal eine Variante noch nicht unterstützt wird, können Kunden unter Wartung die Unterstützung dafür kostenlos anfordern.

Neben diesen Standardtests sind auch zusätzliche sogenannte Cluster- und Script-Tests möglich, die beim Test komplexerer Schaltungen auf der Karte nötig sind, auch wenn deren Bauteile nicht direkt Boundary-Scan-fähig sind. Der Aufwand für die gesamte Testplanerstellung hängt von der Komplexität der Baugruppe ab und schwankt zwischen einem Tag und einigen Wochen (für sehr komplexe Designs, deren Schaltungsentwicklung mehrere Mannmonate oder -jahre betrug). Der Hersteller bietet die Erstellung von Testplänen auch als Dienstleistung an.

Kombination mit Funktionstests

Bei komplexeren Baugruppen ist die Kombination von JTAG/Boundary-Scan- und Funktionstests durchaus sinnvoll. Viele Prozessoren lassen sich über ihre JTAG-Schnittstelle nicht nur im Boundary-Scan-Modus betreiben, sondern auch in einem funktionalen Debugging-Modus. Hierbei werden Testprogramme über die JTAG-Schnittstelle auf den Prozessor geladen und ausgeführt. »ScanExpress JET« (JTAG Embedded Testing) von Corelis integriert diese Funktion in das Testwerkzeug. Generell stehen im Rahmen der »ScanExpress«-Familie viele verschiedene Controller mit USB-, Ethernet-, PCIe- und CPCI/PXI-Schnittstellen sowie einem bis 32 JTAG-Taps bereit.

Über den Autor:

Burkhard Jour ist Sales Manager bei A.R. Bayer DSP Systeme.

Design for Testability

Einige Voraussetzungen sind bei der Schaltungsentwicklung zu beachten, damit die Baugruppe später mit Boundary Scan getestet werden kann:

- Es muss mindestens ein Boundary-Scan-fähiges Bauteil auf der Baugruppe sein,

- die Boundary-Scan-fähigen Bauteile müssen in einer oder mehreren JTAG-Ketten miteinander verbunden sein und die JTAG-Anschlüsse jeder Kette auf einen Stecker herausgeführt sein und

- manche Bauteile erfordern bestimmte Pegel an bestimmten Pins, um Boundary-Scan-fähig zu sein.

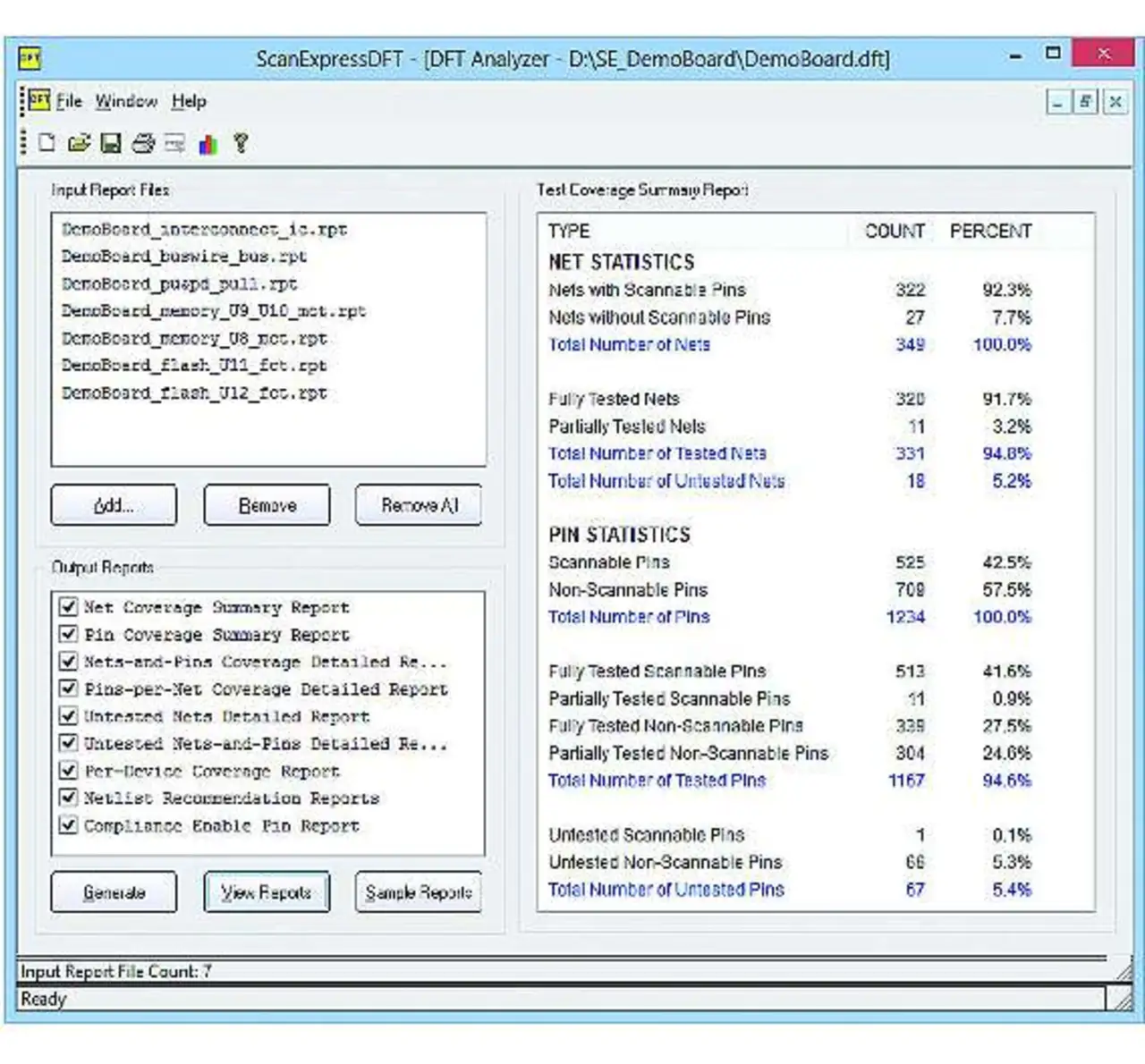

All diese Voraussetzungen überprüfen die »ScanExpress«-Werkzeuge schon während der Baugruppenentwicklung noch vor dem Layouten. Zudem bieten die Tools eine Design-for-Testability-Analyse (Bild 7), mit der sich die Testtiefe analysieren lässt, sodass der Entwickler gegebenenfalls noch rechtzeitig die Möglichkeit hat, diese durch Designoptimierungen weiter zu verbessern.