WiMAX Mini-PCI Modul ermöglicht Endgeräte für unter 100 Dollar

Fortsetzung des Artikels von Teil 1

Motorola mit Flash-Speicher und EEPROM

Das schwächste Segment des Controller-Spezialisten Motorola [3] ist zwar das 16-bit-Segment, aber dennoch hat das Unternehmen auch hier eine Menge zu bieten. Bei den 16-Bittern hat Motorola (Rang 4) vier Familien im Programm: Die klassischen M68HC16- und M68HC12-Familien, die moderne HCS12-Familie und die Controller-/ DSP-Familie DSP56800. Rechnet man die speziellen Derivate für Automobilanwendungen – HCS12 Automotive und M68HC12 Automotive – separat, dann sind es sogar sechs Familien. Das neueste Arbeitspferd ist die HCS12-CPU, die bei einer Taktfrequenz von 25 MHz mit einer minimalen Befehlszykluszeit von 40 ns aufwartet. Bei dieser Nachfolgegeneration der 68HC12-Familie, die in einem 0,25-µm-Prozess gebaut wird, bietet der Hersteller einen kompletten Baukasten moderner Peripheriemodule und umfangreiche Speicheroptionen an.

Jobangebote+ passend zum Thema

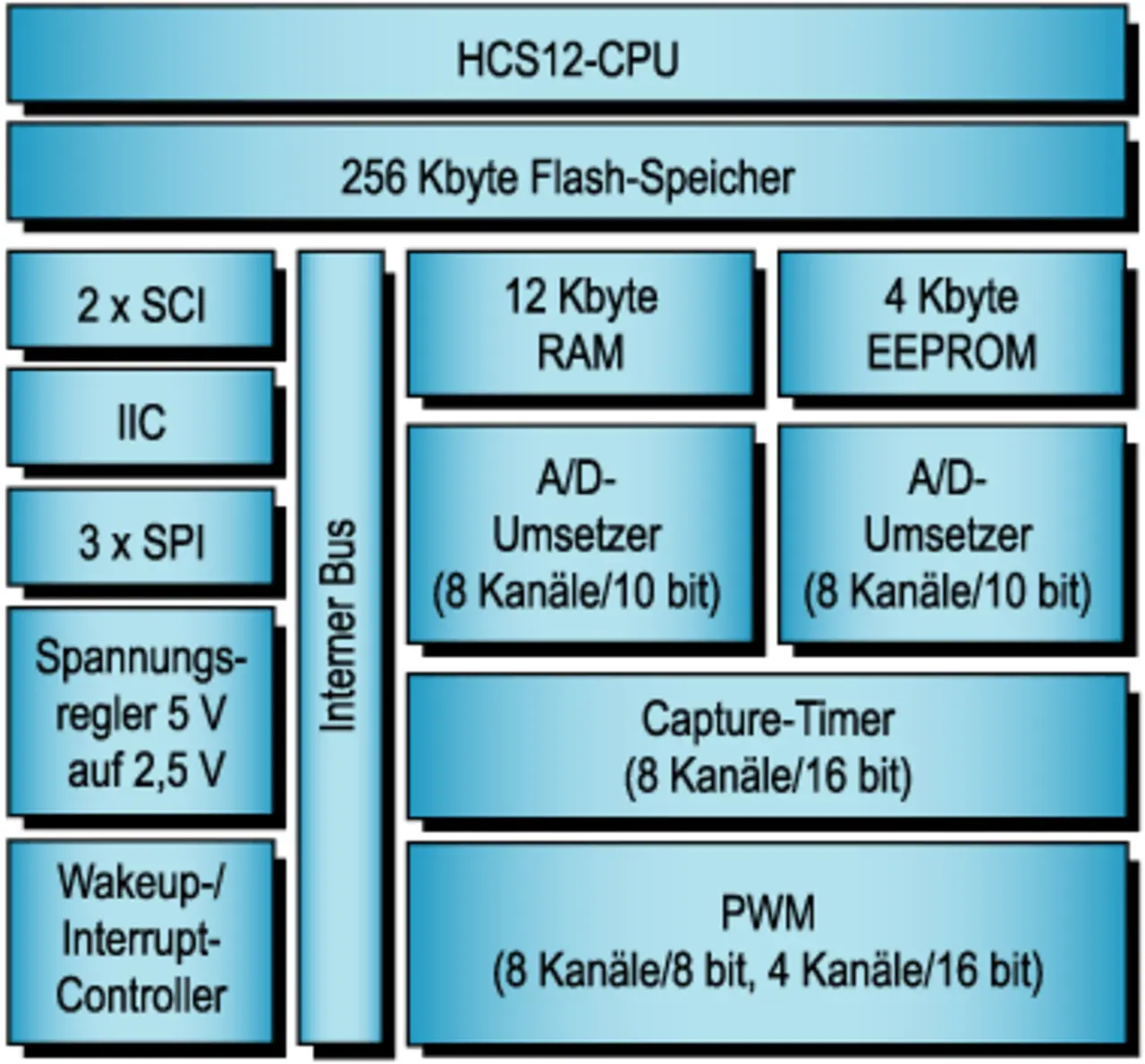

Der MCS9S12A256 (Bild 4) ist ein Baustein, gedacht für Applikationen wie Instrumentierung, Energie-Management, industrielle Steuerungen und Sicherheitssysteme, der recht gut den momentanen Stand der Technik widerspiegelt: Neben der HCS12-CPU integriert der Chip 256 Kbyte Flash-Speicher, 4 Kbyte EEPROM und 12 Kbyte RAM. Der Flash-Speicher kommt mit einer Programmier- und Löschspannung von 5 V aus und benötigt für eine komplette Programmierung weniger als 10 Sekunden. Es stehen vier unabhängig programmierbare Flash-Speicherfelder zur Verfügung, wobei sich jeweils 512 byte große Blöcke löschen (20 ms) und 2 byte große Einheiten programmieren lassen (20 µs im Burst-Modus). Das EEPROM benötigt eine Programmierzeit von 46 µs, wobei sich 4 byte auf einmal löschen und 2 byte auf einmal schreiben lassen. Die Peripherie umfasst diverse Schnittstellen, wie zwei SCI (Serial Communications Interface), I2C und drei SPI (Serial Peripheral Interface), zwei achtkanalige A/D-Umsetzer mit 10 bit Auflösung, einen Spannungsregler für 2,5 bis 5 V, einen Pulsbreiten-Modulator, der sich entweder als 8 Kanal/8 bit oder 4 Kanal/16 bit konfigurieren lässt, und einen „Enhanced Capture Timer“ mit acht Kanälen und 16 bit Auflösung. Um die Takterzeugung kümmert sich ein Timer-Modul mit PLL und Teiler. Für den Baustein stehen zwei Gehäuse mit bis zu 91 I/Os zur Verfügung: ein 80-Pin-QFP sowie ein 112-Pin-LQFP.

Toshiba mit 32-bit-Upgrade-Pfad

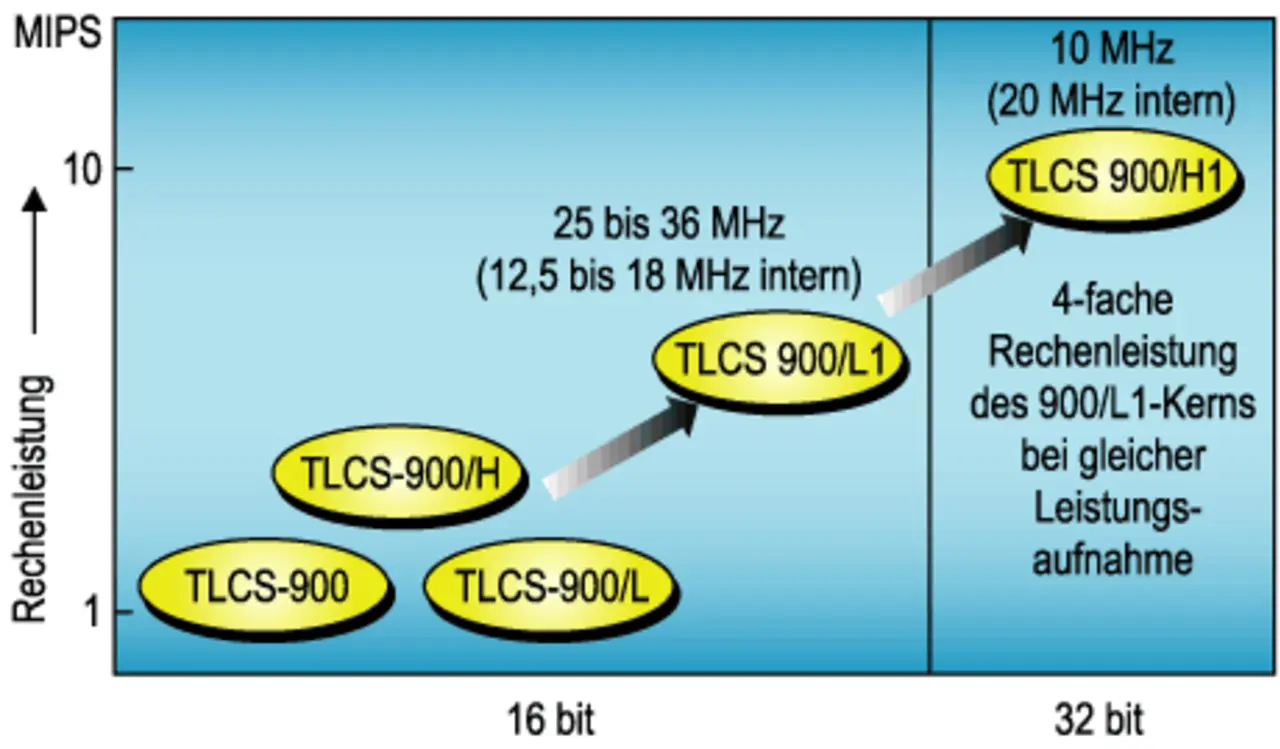

Die japanische Toshiba (Rang 5, [4]) hat verschiedene Familien um die TLCS-900-Architektur (Bild 5) entwickelt, die sich durch ein 32-bit-Register-System und einen linearen Adressraum von 16 Mbyte auszeichnet: Die Familie 900/L zielt mit einem Betriebsspannungsbereich von 2,7 bis 5,5 V und einer minimalen Befehlszykluszeit von 200 ns auf portable Anwendungen, die wenig Leistung aufnehmen sollen. Für höhere Rechenleistungen, wie sie Büroanwendungen fordern, ist die 900/H-Familie mit einer minimalen Befehlszykluszeit von 160 ns und eingebauter DRAM-Schnittstelle gedacht. Die neueste Familie 900/L1 mit einer minimalen Befehlszykluszeit von 111 ns bei externen Taktfrequenzen bis zu 36 MHz (intern 18 MHz) ist hingegen nicht nur viermal schneller, sondern auch 70 % sparsamer als die 900/L-Familie. Die Derivate der L1-Familie bieten bis zu 256 Kbyte Flash-Speicher und neben gängigen Peripheriemodulen, wie Timern, seriellen Schnittstellen, A/D-Umsetzern etc., auch ungewöhnliche Funktionen, wie LCD- und DRAM-Controller. Für Applikationen, die mit der Rechenleistung eines 16-Bitters nicht mehr auskommen, gibt es die Befehlssatz-kompatible 32-bit-CPU 900/H1, die mit der vierfachen Rechenleistung eines 900/L1 bei gleicher Leistungsaufnahme aufwartet.

- WiMAX Mini-PCI Modul ermöglicht Endgeräte für unter 100 Dollar

- Motorola mit Flash-Speicher und EEPROM

- Platz 6 bis 10 mit 20 Prozent Marktanteil