Netzwerkprozessoren: 8 Cores auf einem Chip

Fortsetzung des Artikels von Teil 2

Netzwerkprozessoren: 8 Cores auf einem Chip

Byte Channel Services

Jobangebote+ passend zum Thema

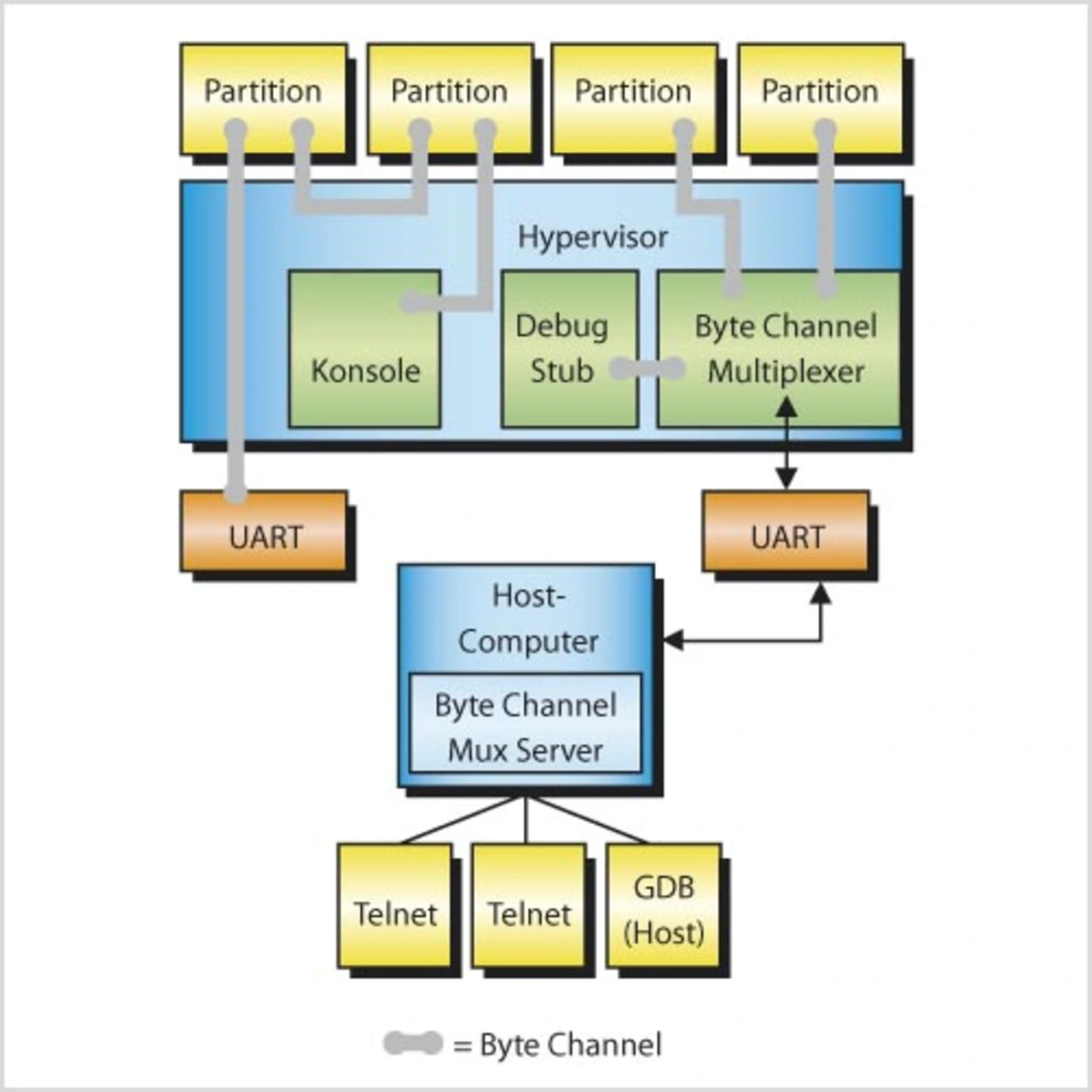

Der Hypervisor verfügt über den „hcall“-basierten Dienst „Byte Channel“, der einen interrupt-gesteuerten zeichenbasierten I/O-Kanal öffnet (Bild 4).

Diese Funktion ähnelt der eines UART. Über die Byte Channels kann etwa jede Partition über eine Konsole verfügen. Jeder Byte Channel arbeitet mit einem „End Point“, wobei ein flexibler Satz von End Points unterstützt wird:

- ein „Byte Channel to UART“-Multiplexer,

- ein physikalischer UART auf dem QorIQ-Prozessor der P4-Baureihe,

- ein weiterer Byte Channel End Point,

- ein Hypervisor Debug Stub,

- die Hypervisor-Konsole.

Mit dem „Byte Channel to UART“-Multiplexer lassen sich mehrere Byte Channel Streams multiplexen und über einen physikalischen UART an ein Host-System ausgeben. Auf dem Host-System läuft ein MUX-Server, der die Streams demultiplext und diese über Netzwerk-Ports ausgibt.

Weitere Hypervisor-Dienste

Darüber hinaus bietet der Hypervisor die folgenden „hcall“-basierten Dienste:

- Interrupt Controller Services für die Verarbeitung und Koordination von Hardware Interrupt Services.

- Inter-Partition Doorbell Services, mit denen eine Partition einen Interrupt an eine andere Partition senden kann.

- GPIO Services, mit denen die Partitionierung bzw. die Zuordnung einzelner Universal-I/O-Pins zu Partitionen erfolgen kann.

- Power Management Services, mit denen Partitionen die Energiesparfunktionen des QorIQ-Kommunikationsprozessors aktivieren und verwalten können.

Boot-Architektur

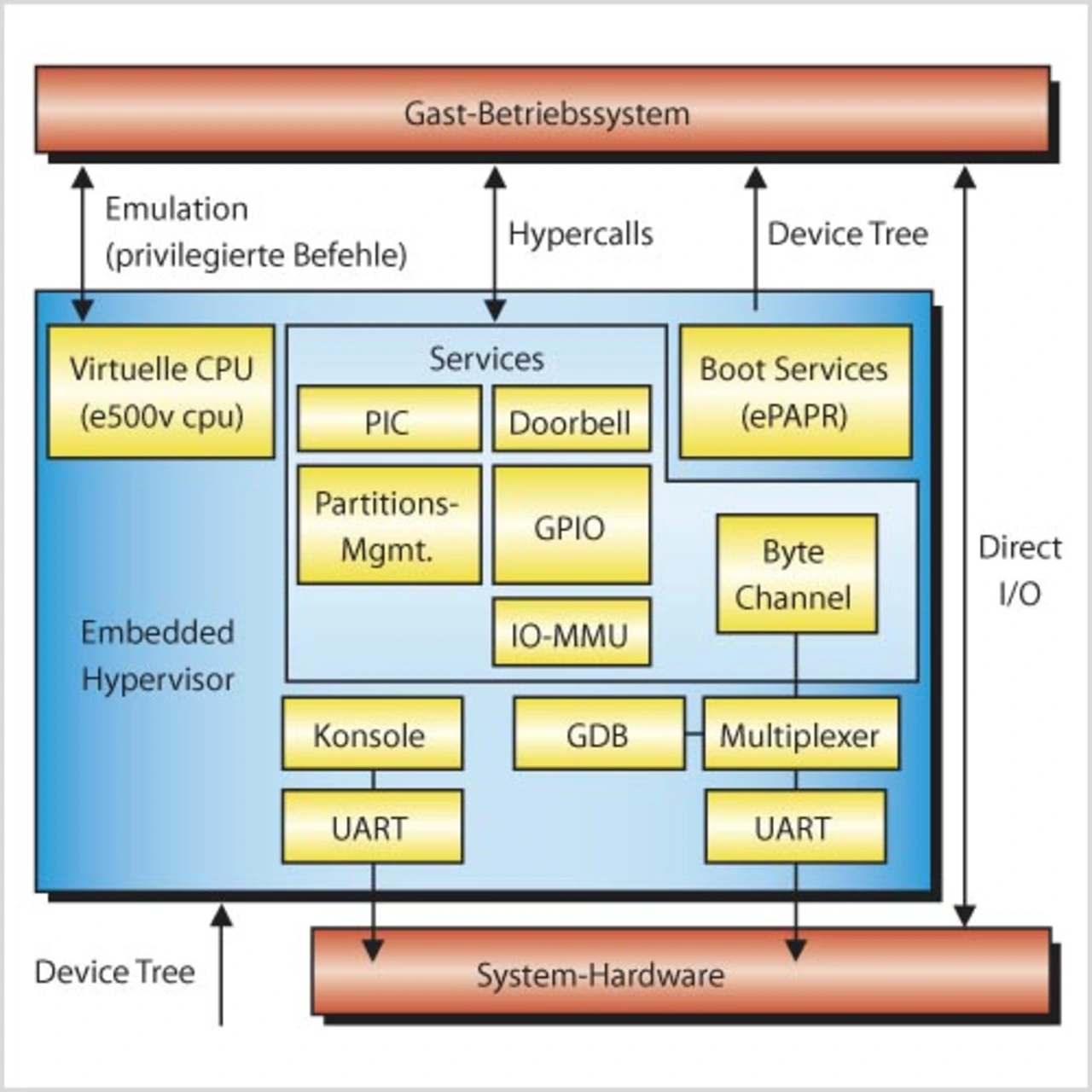

Dem „Embedded Hypervisor“ liegen die Embedded Power Architecture Platform Requirements (ePAPR) von Power.org zugrunde. Diese Architektur definiert zwei Verfahren, mit denen Betriebssysteme gebootet werden könne: „Device Trees“ und „Multi-CPU Boot“. Ein Device Tree ist eine Datenstruktur, die beim Booten an ein Gast-Betriebssystem übergeben wird und mit der die physikalischen und virtuellen Ressourcen definiert werden, welche die Partition ausmachen. Der Device Tree bestimmt, wie ein Betriebssystem herausfindet, über welche Ressourcen es verfügen kann. Der „Multi-CPU Boot“ definiert, wie sich untergeordnete CPUs aktivieren lassen (Bild 5).

Ein QorIQ-Multi-Core-Prozessor der P4-Baureihe lässt sich so konfigurieren, dass er die von einer System-Anwendung gestellten Anforderungen stets erfüllen kann. Die „CoreNet Fabric“-Struktur ist dabei eine der Schlüsselkomponenten der QorIQ-Prozessor-Plattform. Innerhalb des Chips ermöglicht sie weitgehend skalierbare Kommunikationspfade. Eingehende und abgehende Daten können an beliebigen Punkten der Matrix – und nicht nur über einen einzigen Zugang – in das System eingespeist werden bzw. dieses verlassen. Buskonflikte, Engpässe und Latenzprobleme, die durch eine Skalierung gemeinsamer Bus- und Speicher-Architekturen auftreten, können so erst gar nicht auftreten.

Dank der „CoreNet Fabric“, einer dreistufigen Cache-Hierarchie und der neuartigen Virtualisierungsfunktionen des „Embedded Hypervisor“ können die e500mc-Kerne zu einem vollständig symmetrischen Multi-Prozessor-“System on Chip“ kombiniert werden. Natürlich lassen sie sich auch mit unterschiedlichsten Abhängigkeitsgraden zu einem AMP-System (Asymmetric Multiprocessing) konfigurieren.

Das neue Virtualisierungsverfahren eröffnet durch den „Embedded Hypervisor“ eine neue Dimension der Hardware-Partitionierung. So kann sichergestellt werden, dass die auf einer beliebigen CPU laufende Software nur diejenigen Ressourcen nutzt, die ihr explizit zugeteilt sind. Der „Embedded Hypervisor“ gewährleistet einen sicheren und autonomen Betrieb mehrerer Betriebssysteme und macht es möglich, dass sie sich die Systemressourcen teilen; dazu zählen etwa Prozessorkerne, Speicher und andere auf dem Chip integrierte Funktionsblöcke.

Die Möglichkeit, unterschiedliche Betriebssysteme auf den Kernen laufen zu lassen, bietet eine erhebliche Flexibilität, was Partitionierung, Datenpfade und Verarbeitung der Anwendung betrifft. Darüber hinaus vereinfacht sich dadurch die Konzentration von Funktionen. Was bisher auf mehrere diskrete Prozessoren verteilt werden musste, kann nun in einem einzigen Baustein verarbeitet werden. jw

| Gary Whisenhunt |

| Stuart Yoder hat seinen Bachelor of Science im Fach „Computer Science and Engineering“ an der LeTourneau University erworben. Er ist „Software Architect“ bei Freescale und hat leitet dort die technische Entwicklung der „Embedded Hypervisor“-Software für die „QorIQ P4 Multi-Core“-Kommunkationsplattform mit den Rechnerkernen der Power-Architektur. Seit 18 Jahren schreibt er Software, vor seiner Anstellung bei Freescale war er bei IBM und Intel tätig. stuart.yoder@freescale.com |

- Netzwerkprozessoren: 8 Cores auf einem Chip

- Netzwerkprozessoren: 8 Cores auf einem Chip

- Netzwerkprozessoren: 8 Cores auf einem Chip

- Debuggen