Hochleistungskommunikation über problematische Medien

10-Gbit/s-Ethernet: Die zweite Generation

Fortsetzung des Artikels von Teil 3

10-Gbit/s-Ethernet: Die zweite Generation

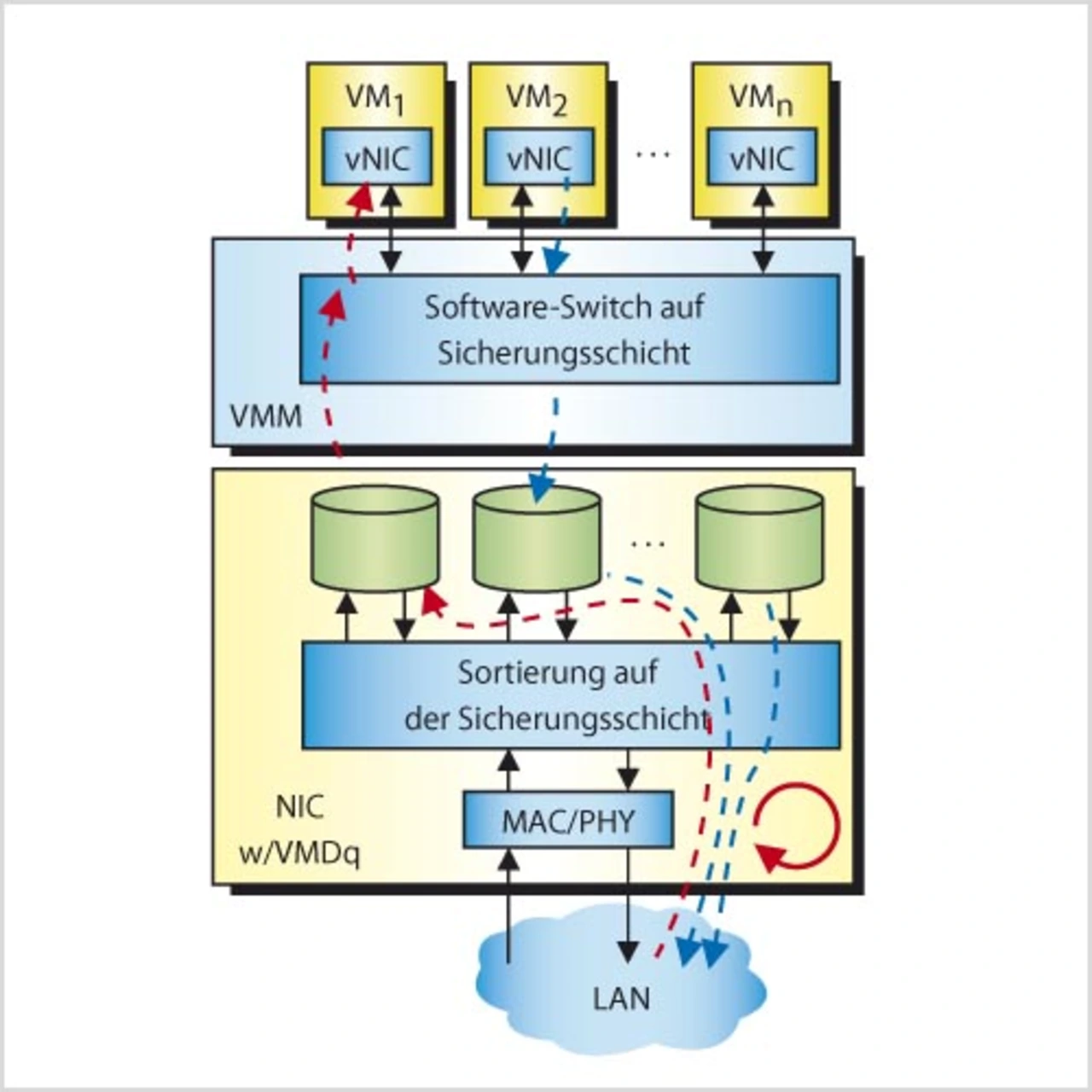

Der 82598 wurde im Hinblick auf die Zusammenarbeit mit Intels Dual- Core-Server-Prozessoren entwickelt, die in einer „Virtualization“-Anwendung betrieben werden. Dieser von der Firma Intel geprägte Begriff bezeichnet den Einsatz mehrerer unabhängiger Betriebssysteme auf einem PC, die separate Festplatten-Partitionen oder mehrere CPU-Kerne für ihren Betrieb nutzen. Für eine Entlastung der Host-Prozessoren von der „Netzwerk- Arbeit“ haben die Intel-Ingenieure auf diesem Chip eine breite Auswahl von Mechanismen implementiert, die unter der generellen Bezeichnung „Host Offloading“ zusammengefasst sind. Hierzu zählen 16 „Virtual Machine Device“-Warteschlangen, mit denen sich die Datenpakete in einer „virtualized“ Umgebung effizient routen lassen und sich eine gewisse „Fairness“ bei der Zuteilung der Ressourcen für eine Datenübertragung sicherstellen lässt. Die Implementierung eines „MSI-X Support“ reduziert den Aufwand für die Verwaltung von Interrupts, durch eine Art Load Balancing lässt sich die Belastung ausgleichen, die durch die Behandlung der Interrupts von mehreren Cores entsteht (Bild 3).

Jobangebote+ passend zum Thema

Zu den implementierten Verfahren für eine Minimierung der Paket-Verarbeitungszeit – bekannt als „TCP Offload“ – gehören eine „Header split and replication in receive“-Routine, die Unterdrückung der Prüfsummen-Routine für TCP und UDP bei der Paket- Inspektion sowie das Ignorieren der Header-Informationen bei der Segmentierung von TCP-Datenpaketen für IPv4 und IPv6. Schließlich werden auch die bei IPv6 zusätzlich hinzugekommenen Header-Information unberücksichtigt gelassen, soweit diese für die Inspektion und Klassifizierung der Datenpakete und das Auslesen der Routing-Informationen unerheblich sind.

Die beiden Media Access Controller unterstützen die 10GbE-Schnittstellen- Varianten CX-4 (Twin Axial Copper Cabling für 15 m Länge – IEEE 802.3ak) und KX4/KX (IEEE 802.3ap). Jeder Port ist mit einem Seriell/ Parallel-Umsetzer (SerDes) ausgestattet, der die Rückwärts-Kompatibilität bei Backplanes sichert, die den 1-Gbit/s-Ethernet-Standard verwenden. Der Chip kommuniziert mit einem „Board Management Controller“- Chip auf der Network Interface Card (NIC) über den System Management Bus (SMBus) oder über die serielle Schnittstelle NC-SI (Network Controller Serial Interface), wie sie von der Distributed Management Task Force (DMTF) definiert wurde [5]. In erster Linie wird der neue Netzwerk-Controller, so jedenfalls die Marketing- Spezialisten von Intel, bei der Anbindung von iSCSI-Speichersystemen über 10-Gbit/s-Ethernet zum Einsatz kommen. Hierzu wurde auch eine iSCSI-Boot-Routine implementiert, die einen „Boot“ über ein iSCSI-Speichersystem erlaubt.

Ohnehin wird die Anbindung von iSCSI-Speichersystemen über 10GbE als Möglichkeit gesehen, eine Alternative zu den eingeführten Fibre-Channel- Übertragungsstandards (FC) der Storage Area Networks (SAN) zu bieten. Der Übergang von SAN zu NAS (Network Attached Storage) wird sich dabei, wie bei jeder „Infrastruktur- Technologie“, nicht schlagartig vollziehen. Ende 2006 waren nach Angabe der Firma NetApps [6] vornehmlich in Windows-Umgebungen 22 000 so genannter IP-SANs – also Speichersysteme mit iSCSI-Festplatten – in Betrieb. Es wird erwartet, dass ein Großteil der künftigen iSCSI-Speichersysteme mit einer 10GbE-Schnittstelle ausgestattet wird. Die Idee dabei ist, über einen 1/10-Switch zehn Server mit einer 1-Gbit/s-Ethernet-Schnittstelle an ein Speichersystem anzubinden.

Verbindungen über Glas und Kupfer

Für die Bitübertragungsschicht des 10-Gbit/s-Ethernet-Standards haben die IEEE-Komitees mehrere Varianten spezifiziert, die in der IEEE 802.3an beschrieben sind.

- 10GBase-SR beschreibt eine Übertragung mit der vollen Datenübertragungsrate von 10,3 Gbit/s über einen Kanal per 50/62,5-μm-Mehrmoden- Lichtwellenleiter bei einer Wellenlänge von 850 nm. Die Reichweite beträgt 300 m.

- 10GBase-LX4 definiert ein CWDM (Coarse Wavelength Division Multiplexing) über vier optische Kanäle im Bereich 1300 nm, verwendet wird ein 50/62,5-μm-Mehrmoden-Lichtwellenleiter. Die Datenübertragungsrate pro Kanal sinkt auf 3,125 Gbit/s, die Reichweite beträgt 300 m; für Reichweiten bis 10 km ist eine Übertragung über Ein-Moden-Lichtwellenleiter spezifiziert.

- 10GBase-LRM benötigt wie die SRSpezifikation keine Modifikation des 10-Gbit/s-Datenstroms; um die Reichweit zu verbessern wird hier senderseitig die Dispersion des Lichtwellenleiters elektronisch kompensiert (EDC – Electronic Dispersion Compensation). Die Reichweite sollte auch hier zunächst 300 m betragen, später wurde sie auf praktikable 220 m reduziert.

- 10GBase-CX4 verwendet als „Kupfer“- Übertragungsstandard das im Infiniband- Standard spezifizierte Kabel mit acht Adernpaaren, auch die Datenübertragungsrate ist mit 3,125 Gbit/s nach Vorbild des Infiniband gewählt, die Reichweite liegt bei 15 m.

- 10GBase-T ist der Basisstandard für die drahtgebundene Übertragung. Es werden vier Adernpaare verwendet, die Übertragungslänge reicht bis 55 m (mit CAT6e-Kabel).

- 10-Gbit/s-Ethernet: Die zweite Generation

- 10-Gbit/s-Ethernet: Die zweite Generation

- 10-Gbit/s-Ethernet: Die zweite Generation

- 10-Gbit/s-Ethernet: Die zweite Generation