European processor technology

Production of RISC-V test chip starts

Europe wants to become independent in HPC chip manufacturing in the long term. To achieve this, the European Processor Initiative was launched. Now it is reporting its first success.

The EPI – European Processor Initiative – is a project with 28 partners from 10 European countries. The project aims to make the EU less dependent on exports for HPC chips and infrastructure. For this reason, the members are researching test chips for series production. A first success has now been announced: The test chip »EPAC1.0« has been released for production.

In the project, the partners want to provide processor IPs based on RISC-V called EPAC – European Processor Accelerators – that have been developed entirely in Europe. Using the RISC-V architecture, it is possible to use open-source resources at the hardware architecture and software level. This should enable independence from non-European technologies.

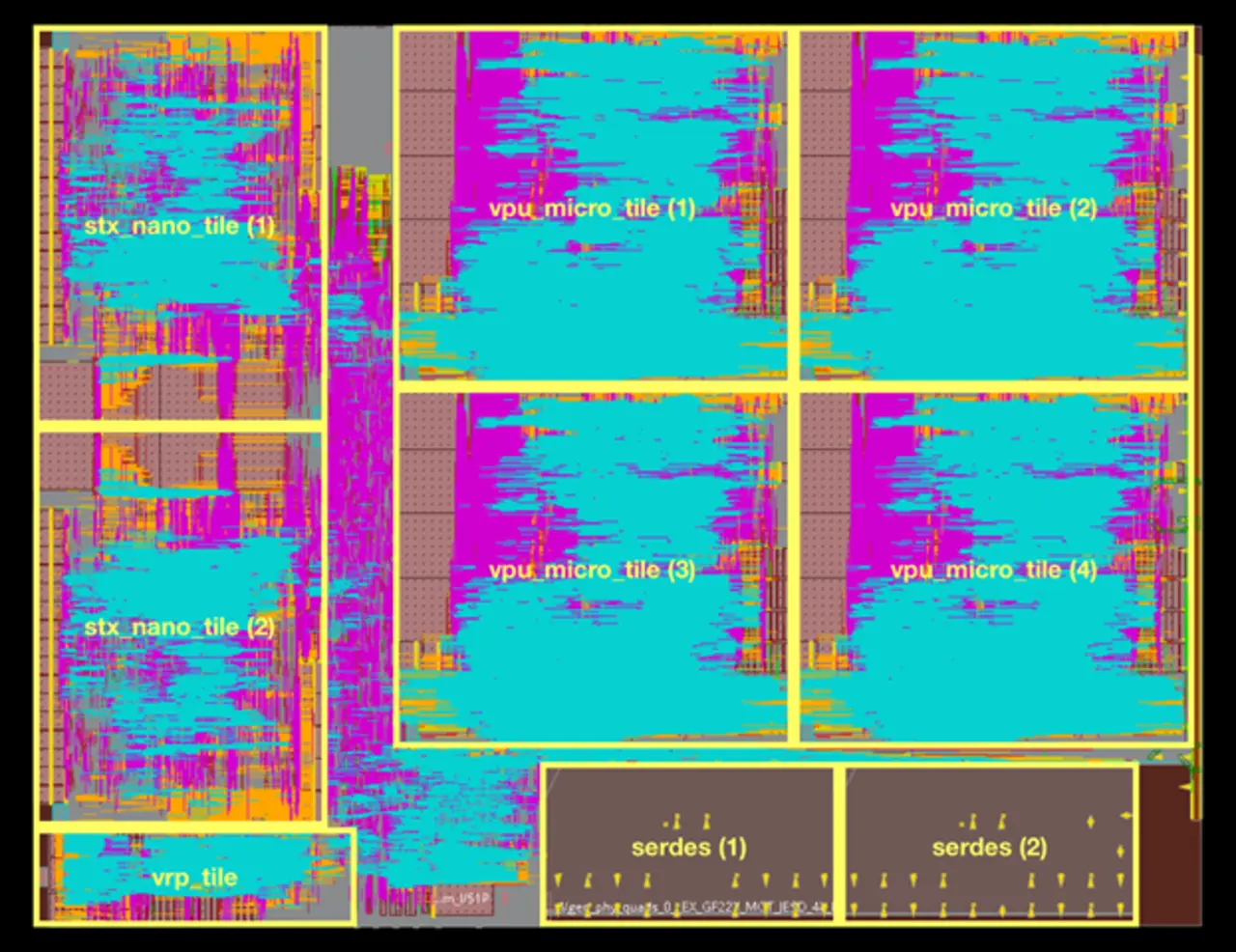

Four VPUs and a RISC-V core

EPAC combines several accelerators specialized for different application domains. The test chip, shown in Figure 1, contains four vector processing micro-tiles (VPUs) consisting of an Avispado RISC-V core from SemiDynamics and a vector processing unit from the Barcelona Supercomputing Center and the University of Zagreb. Each tile also contains a home node and an L2 cache, developed by Chalmers and Forth, respectively, which provide a coherent view of the memory subsystem. The Stencil and Tensor Accelerator (STX) was developed by Fraunhofer IIS, ITWM and ETH Zurich, and the Variable Precision Processor (VRP) by CEA LIST. They are connected with a Network on Chip and SERDES technology from Extoll.

The EPAC design was fabricated by Fraunhofer IIS for chip integration in Globalfoundries 22FDX low-power technology. It will be integrated into the FPGA-based board designed by Forth and the University of Zagreb.

As a next step, the project partners aim to further improve the next generation EPAC accelerator and interfaces to achieve even higher performance as well as lower power consumption in 12nm technology and below. This is to be achieved with a chiplet approach.