New RISC-V processor family

From microcontroller to multicore processor

The latest announcement of a strategic partnership with Renesas opened the door for RISC-V startup SiFive into the club of established semiconductor manufacturers. With its Series 7 processors, SiFive bridges the gap from microcontroller to multicore processor, which is anything but trivial.

The announcement was spectacular: SiFive, the largest supplier of processor IP based on RISC-V microarchitecture, but still with the image of a startup, will become a strategic partner of Renesas – and that also for high-end automotive applications in the field of ADAS (Advanced Driver Assistance Systems) and autonomous driving. »The SiFive RISC-V portfolio is silicon proven and available in leading and advanced manufacturing foundries, offering flexibility to customers and partners,« Renesas stated, and with that at the latest, SiFive was promoted to the circle of established IP providers.

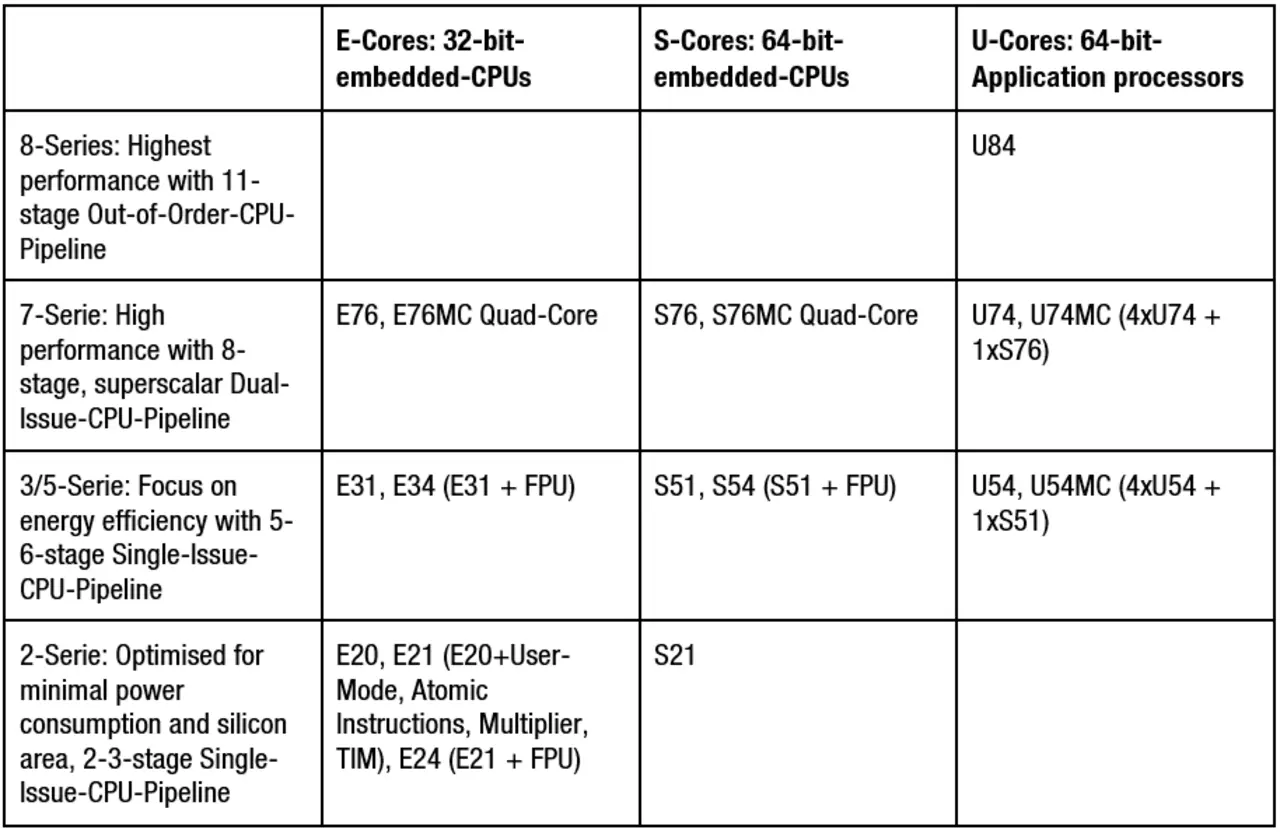

In terms of flexibility, SiFive already offers an amazingly broad range of processor IP. In addition to 32- and 64-bit standard cores with a focus on embedded applications (table), software and hardware for accelerating AI/ML applications with SiFive AI ISA extensions and RISC V vector extensions have recently been offered under the name »SiFive Intelligence«.

The widest arc is the Processor Series 7, which bridges the gap from microcontroller to microprocessor and is certainly of great interest to embedded developers.

The dual-issue in-order processor core is in the same complexity as e.g. Arm's Cortex-A55. SiFive offers versions for real-time embedded processing as well as for Linux applications.

At the high end of the performance scale is the new U74MC IP core, which builds on the U54 and already offers multicore configurations and Linux compatibility. The U74MC features a double precision floating point unit (FPU) as standard. Up to nine of the 64-bit cores can share an L2 cache with ECC protection. For embedded applications, there is the 32-bit E76 and the 64-bit S76, which contain an FPU that calculates with single precision. With 4.9 CoreMark/MHz and a clock frequency that is around 10 % higher than the predecessor Series 5, users get significantly higher computing performance with the Series 7. In addition, there are further improvements to the memory subsystem compared to the Series 5:

- Zero clock cycle load-to-use latency, instead of 1 clock cycle,

- 2 clock cycles access time to the SRAM in the worst case, instead of 5 clock cycles, and

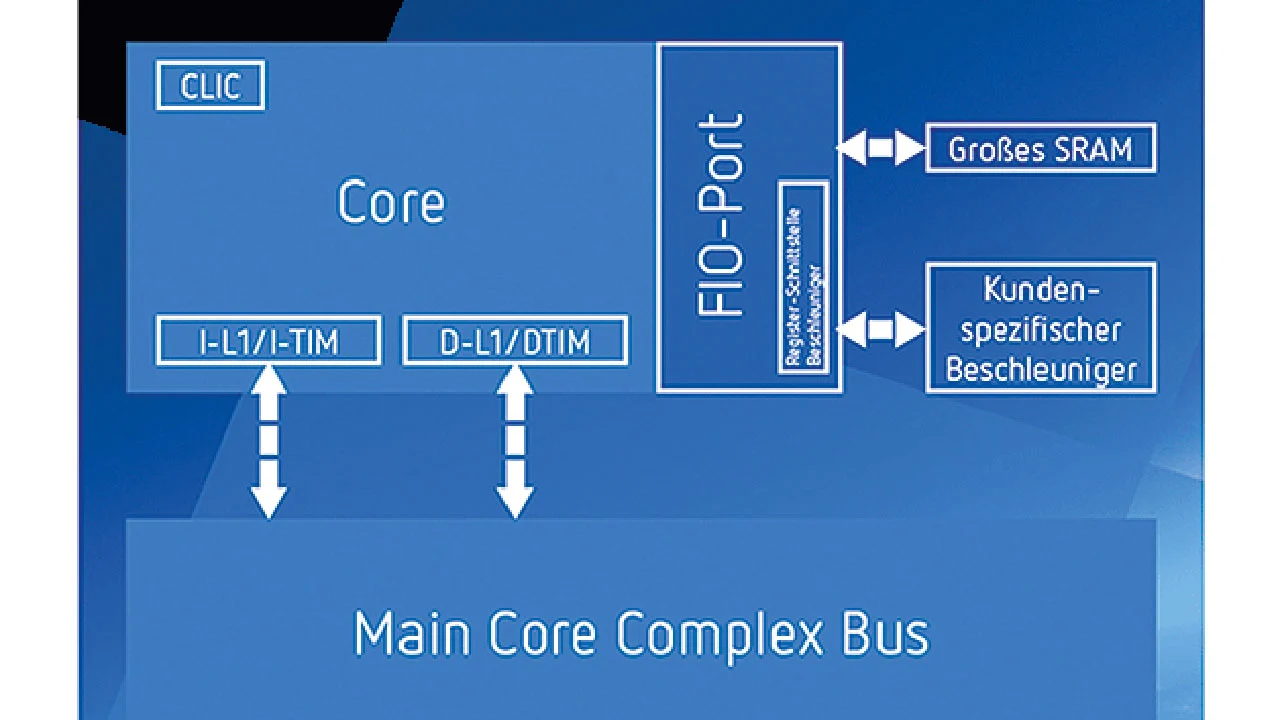

- a fast I/O port, called Fast I/O or FIO for short. This is tightly coupled to the core and enables core-to-memory and low-latency accelerator operations. The FIO port can also be used to incorporate larger SRAM as well as custom accelerators via the accelerator register interface (Figure 1).

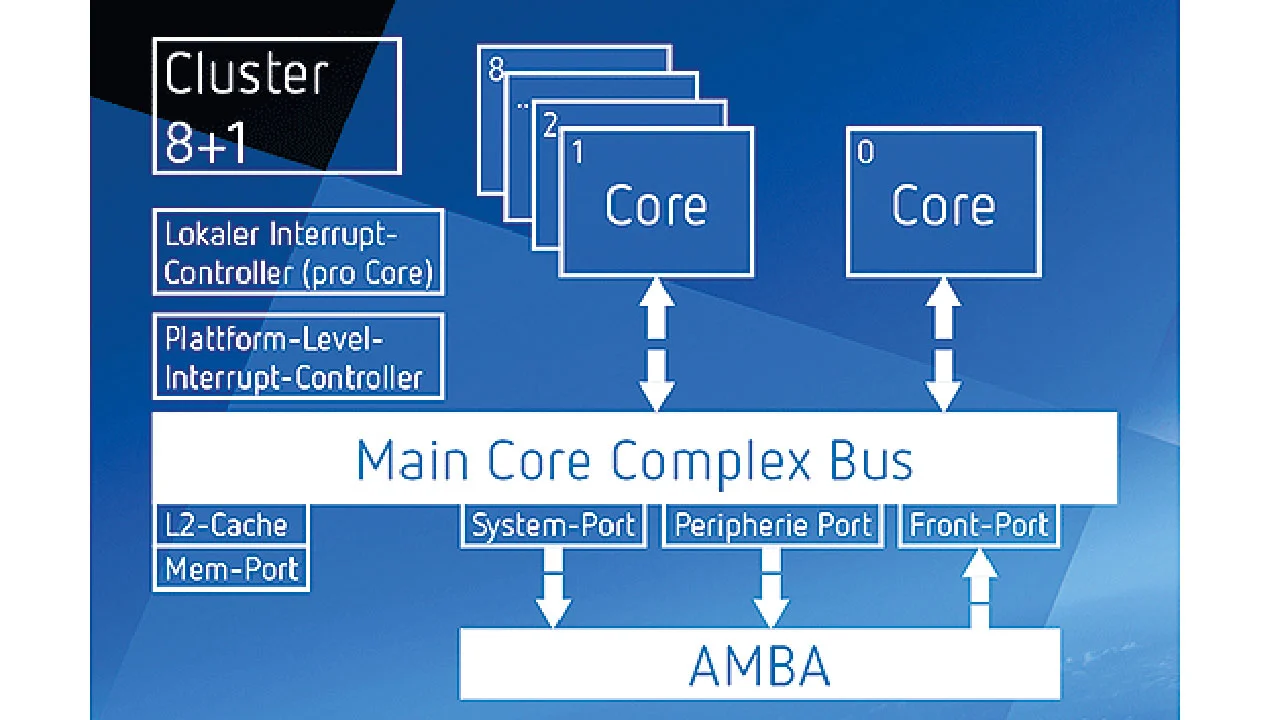

In the end, the 7 series processor achieves a 63 % improvement in CoreMarks/MHz (4.9 CM/MHz). The basis of the 7 series is a cluster with up to nine CPUs (8+1, Fig. 2). The cores can be a mix of the Series 7 cores as well as other existing processor cores from SiFive. All elements in the cluster are cache-coherent - including all advanced SRAM options as well as any custom accelerators attached to the cores. The cluster can be further scaled by using AMBA, which allows integration of up to 64 clusters on a single chip. Multi-chip support is also possible via ChipLink.

Following a $50 million funding round realized in April 2018, SiFive had expanded its focus to IP for embedded applications at the time. Part of the differentiation of SiFive IP is undoubtedly its configurability. Customers can start with the specification for a standard core and add or remove standard command extensions, change memory details and configure other features.

- From microcontroller to multicore processor

- New CPU in Series 7

- SiFive vs. Arm