Freescale Technology Forum 2012

Neuer CEO Gregg Lowe hält Keynote und macht ARM glücklich

Nur 13 Tage nach seinem Amtsantritt hielt Gregg Lowe vor tausenden Zuhörern seine erste Keynote beim FTF. Neben dem neuen Ultra-Low-Power-Mikrocontroller Kinetis-L hatte er noch weitere interessante Neuigkeiten im Gepäck.

Lowe (Bild 1), den viele Beobachter auf Grund seines jungen Alters und seiner Erfahrung im Top-Management bei Texas Instruments schon als logischen Nachfolger für TIs CEO Richard Templeton gesehen hatten, erklärte zunächst, was ihn zu Freescale gezogen hat: Die Firmenkultur und das Wertesystem von Freescale stimme mit seinen Vorstellungen überein, zudem wolle er dazu beitragen, aus Freescale eine „stärkere Firma“ zu machen.

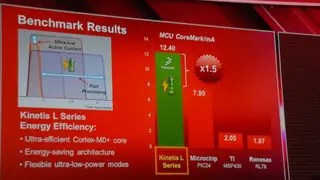

Um zu demonstrieren, dass die neue MCU-Familie Kinetis-L (eine ausführliche Analyse finden Sie hier) nicht nur auf dem Papier energiesparender arbeitet als die 16-bit-Konkurrenz, hat sich Freescale einen Showcase ausgedacht, zu dem Lowe Senior-VP Dr. Reza Kazerunian, Chef des Auto-, Industrie- und Multi-Market-Geschäftes zusammen mit ARMs CEO Warren East auf die Bühne bat (Bild 2). Kinetis-L musste dabei in einer Art Energie-Benchmark gegen die Konkurrenz von TI, Microchip und Renesas antreten.

Jobangebote+ passend zum Thema

Bei dem Versuchsaufbau wird für Kinetis-L, MSP430, PIC24 und RL78 jeweils ein gleich großer Supercap mit einer definierten und identischen Ladung auf gleiche Spannung aufgeladen. Dann wird dieser vom restlichen Versuchsaufbau isoliert, so dass die MCUs ausschließlich aus dem Supercap gespeist werden.

Diese müssen damit so oft es geht den bekannten Benchmark CoreMark von EEMBC bei maximaler Taktfrequenz aus dem Flash-Speicher laden und berechnen. Um den unterschiedlichen Rechenzeiten Rechnung zu tragen, werden die MCUs in den Sleep-Mode überführt, sobald sie fertig sind. Die nächste Berechnung beginnt dann zu einem definierten Zeitpunkt, wenn alle MCUs sicher mit einem Rechendurchlauf fertig sind, nämlich immer nach weiteren 5 Sekunden.

Wie die Bilderstrecke zeigt, geht dem RL78 als erstes die Puste bzw. die Energie aus, was der hohen absoluten Stromaufnahme und der vergleichsweise langen Rechenzeit geschuldet ist. Es folgen MSP430 und PIC24, der Kinetis-L hält am längsten durch, da er dank seiner hohen Rechenleistung den Benchmark in extrem kurzer Zeit abarbeiten und dann in den Sleep-Mode gehen kann. Was bei diesem Showcase freilich nicht berücksichtigt ist, ist die Peripherie – wie energieeffizient A/D-Wandler und Co. im Vergleich sind, bleibt zumindest hier offen.

Kinetis-L ist sparsamer als 16-bit-Konkurrenz

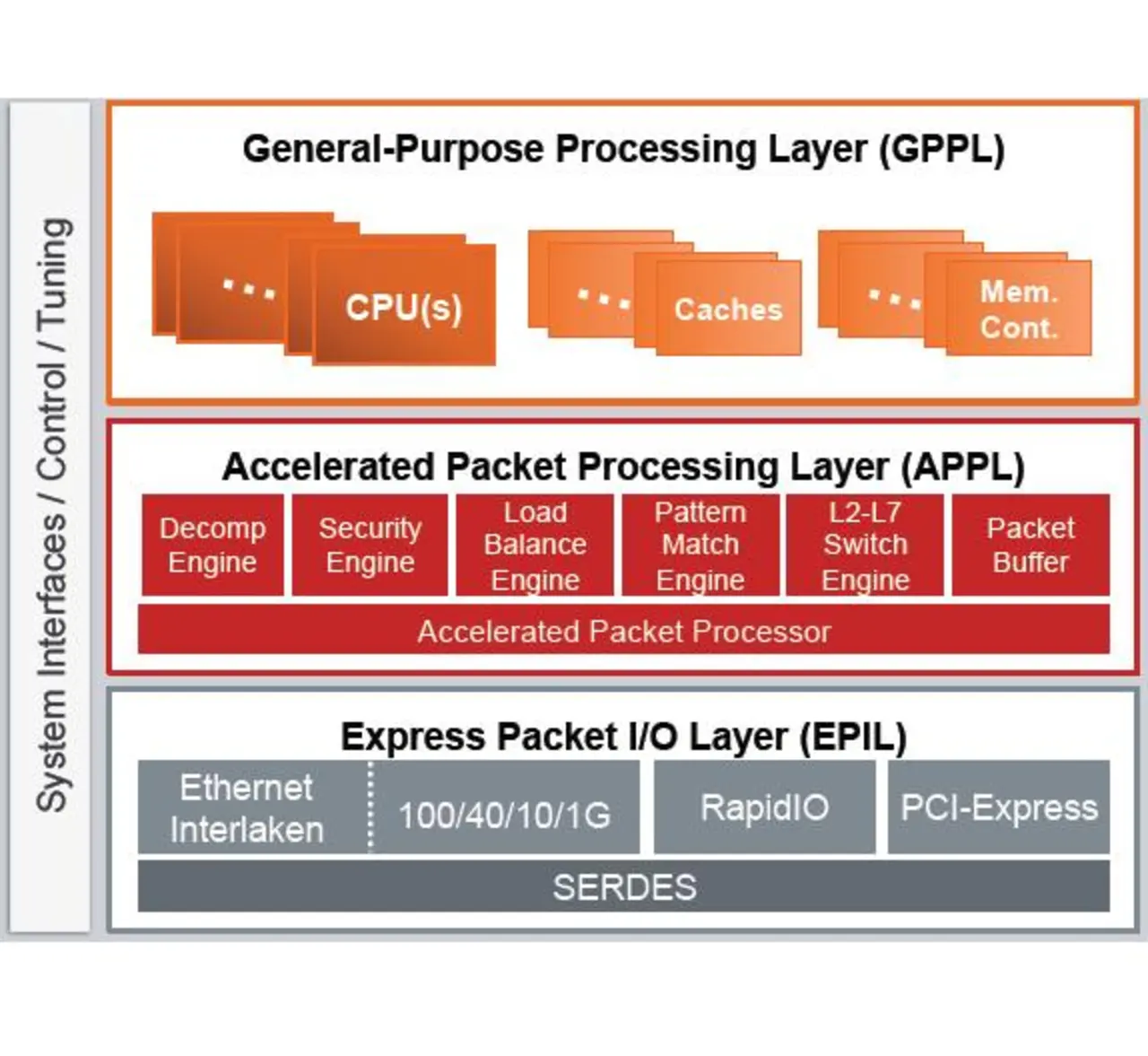

ARMs CEO Warren East war allerdings nicht nur wegen der Einführung der Kinetis-L-MCUs, die als erste Chips überhaupt auf ARMs kleinsten Core, den Cortex-M0+ setzen, sondern auch wegen zwei neuen Kommunikationsprozessoren der QorIQ-Familie glücklich. Die LS-1 und LS-2 genannten Chips setzen nämlich anders als bislang alle Freescale-QurIQ-Prozessoren nicht auf die Power-Architektur, sondern auf ARM-Cores in Form des Cortex-A7 (LS-1) bzw. Cortex-A15 (LS-2). Mit diesen Chips stellte Freescale auch gleich eine neue modulare Architektur mit dem Namen Layerscape vor (Bild 3).

Mit dieser, welche es erlaubt, ARM, PowerPC und Hardware-Beschleuniger für die Paket-Verarbeitung in Hochsprache (C/C++) zu programmieren, wird dank identischer APIs eine hardwareunabhängige Softwareentwicklung ermöglicht.

Die Hersteller von Kommunikationssystemen fordern seit langem, dass die Chip-Hersteller sie bei ihren Bemühungen, eine schnellere Marktreife ihrer Produkte zu erlangen, unterstützen, indem die Software-Entwicklung vereinfacht wird. Heute werden nicht nur Freescales QorIQ-Chips, sondern auch die des Wettbewerbs in Assembler programmiert, z.T. unter Einbeziehung des Chip-Lieferanten für die komplexesten Aufgaben der Datenpaketverarbeitung.

Dieser Trend hat im Kommunikationsbereich zum Einsatz von Allzweck-Cores wie Intels x86 oder ARM-Cores geführt, erst kürzlich hat LSI für seine Basisstationen-SoCs einen Wechsel von PowerPC zu ARM angekündigt.

Mit Layerscape wird nun ein Drei-Schichtenmodell eingeführt (Bild 3), das eine Programmierung in C und C++ ermöglicht – auf Kosten nur marginaler Geschwindigkeitseinbußen gegenüber der Assembler-Programmierung. Mitte 2013 soll das Software-Framework stehen und Muster der LS-1- und LS-2-Chips bereitstehen. Hierbei wartet noch jede Menge Arbeit auf die Texaner, muss die Software-Umgebung doch sowohl das Big-Endian-Modell vom PowerPC als auch das Little-Endian-Modell von ARM unterstützen. Zudem müssen die State-Maschine-Blocks, die für die Beschleunigung der Weiterleitung von Datenpaketen dienen, durch in C programmierbare APIs ersetzt werden, und das vermutlich jeweils einmal für Power und einmal für ARM, selbst wenn die APIs selbst seitens des Aufrufs identisch sind.

Das SoC LS-1 mit zwei jeweils mit 1,2 GHz getakteten Cortex-A7-Cores soll weniger als 3 W aufnehmen, das LS-2 mit zwei 1,6-GHz-Cortex-A15 weniger als 5 W. Beide liefern vermutlich absolut gesehen weniger Rechenleistung als die High-End-Power-basierten Chips, allerdings eine wesentlich bessere Rechenleistung/W.

Auch wenn Freescale betont, auch weiter auf die Power-Architektur zu setzen, wird es vermutlich immer schwieriger, die Entwicklung neuer Power-Cores wirtschaftlich zu rechtfertigen – das kleine Ecosystem um Power gerät zunehmend durch den Kampf Intel gegen ARM, der mittlerweile auch im Kommunikations-Geschäft ausgetragen wird, unter Druck. Durch die weite Verbreitung wird die Power-Architektur vermutlich aber zumindest für die nächste Dekade bestehen bleiben – ggf. auch noch länger.

Last but not least verkündete man auch noch die Bezeichnung für SoCs mit ARMs Cortex-A5 und –M4, deren Technologie wir hier schon vor 4 Monaten beleuchtet haben: Vybrid wird diese Familie heissen, die u.a. in automotiven Intrumenten-Clustern zum Einsatz kommen wird.

Am Ende war allen Zuhörern klar, dass der Zug für Freescale an (fast) allen Fronten in Richtig ARM fährt. Insofern darf man damit rechnen, dass Warren East nach 2010 und jetzt 2012 auch zukünftig sicher noch das eine oder andere Mal beim FTF als Gast auf der Bühne erscheinen wird. Einigkeit herrschte im Publikum auch, was den Auftritt von Neu-CEO Gregg Lowe angeht: Er hatte rundherum überzeugt.