Der LIN-Bus – interessant auch für den industriellen Einsatz

Robust und kostengünstig

Als Standard für die preisgünstige Vernetzung im Automobil hat sich der LIN-Subbus unterhalb von CAN etabliert. Wie schon vorher beim CAN-Bus, beginnt sich die Industrieelektronik nun auch für den LIN-Standard zu interessieren, verbindet der LIN-Subbus doch die Robustheitsanforderungen im Automobil mit kostengünstigen Lösungen.

Als Standard für die preisgünstige Vernetzung im Automobil hat sich der LIN-Subbus unterhalb von CAN etabliert. Wie schon vorher beim CAN-Bus, beginnt sich die Industrieelektronik nun auch für den LIN-Standard zu interessieren, verbindet der LIN-Subbus doch die Robustheitsanforderungen im Automobil mit kostengünstigen Lösungen.

Als neuer Standard für preisgünstige Vernetzungen im Automobilbereich – aber nicht nur dort – wurde im Jahre 2000 LIN (Local Interconnect Network) als Subbus zu CAN etabliert. Der LIN-Bus kann einen Entfernungsbereich bis zu 40 m abdecken, wobei die Daten bidirektional auf einem Draht übertragen werden. Die typische Spannungsversorgung liegt zwischen 8 und 18 V, was seinen Ursprung im Automobilsegment deutlich macht. Als Übertragungsraten sind 2400, 9600 und 19 200 Baud für die Praxis am wichtigsten. Der Bus funktioniert nach dem Master-Slave-Prinzip und kann maximal 16 Slaves umfassen. Die Slaves sind dabei in der Lage, die Geschwindigkeit des Masters zu ermitteln und sich auf diese zu synchronisieren.

Diese Eigenschaften sichern dem LIN-Bus Anwendungsgebiete auch außerhalb des Automobilbereichs, etwa in der industriellen Automatisierungstechnik, in der Gebäudeautomatisierung oder beim Aufbau verteilter Mess- und Regelsysteme im „Low-Cost“-Segment. Ebenso wie der CAN-Bus, der auch vom Automobilbereich ausgehend Anwendungen in den genannten Gebieten fand, profitiert der LIN-Bus von einer stabilen Norm und – dank Massenfertigung – preisgünstigen Komponenten. Seine Leistungsmerkmale – Übertragungsgeschwindigkeit, Teilnehmerzahl und räumliche Ausdehnung – prädestinieren ihn für Anwendungen im unteren Preis- und Leistungssegment, für das CAN oder Ethernet zu teuer und überdimensioniert erscheinen.

Die aufwendige Sicherung der Übertragungsintegrität durch mehrfache Fehlererkennung lässt Anwendungen in problematischen Umgebungen zu. Die Möglichkeit, die Versorgungsspannung der Knoten aus der Busspannung zu gewinnen, erlaubt den Aufbau eines autonomen verteilten Systems, das über ein preiswertes dreiadriges Kabel vernetzt ist.

Selbstverständlich lässt sich das LIN-Bus-Protokoll auf einfachen Mikrocontrollern per Software abwickeln. Allerdings bleibt dann häufig nicht genug Rechenleistung für die eigentlichen Aufgaben des Slave übrig. Aus Sicht des Anwenders wäre eine Lösung ideal, bei der ein einziger Baustein sowohl das LIN-Bus-Interface durch geeignete Hardware unterstützen würde als auch weitere Funktionsblöcke, insbesondere analoge für MSR-Aufgaben zur Verfügung stellen könnte.

LIN-Bus-Knoten auf Basis eines programmierbaren SoC

Einen großen Schritt in diese Richtung geht die hier vorgestellte Lösung auf Basis der Mikrocontrollerfamilie CY8C26xxx von Cypress. Die Bausteine selbst wurden bereits in [1, 2] als Beispiele für FPAAs (Feldprogrammierbare Analog-Arrays) vorgestellt, verfügen aber neben ihren bemerkenswerten analogen Fähigkeiten auch über konfigurierbare digitale Blöcke und eine leistungsfähige 8-bit-CPU. Die digitalen Blöcke erledigen im hier beschriebenen Lösungsansatz die Abarbeitung des LIN-Bus-Protokolls. Dank der dynamischen Rekonfigurierbarkeit wird nur ein geringer Anteil der Ressourcen genutzt, was der eigentlichen Applikation zugute kommt. Schließlich ist noch zu erwähnen, dass die Preisgestaltung dieser Mikrocontroller sehr gut mit dem Preisniveau des LIN-Bus harmoniert.

LIN-Bus-Protokoll

Um die Implementierung verstehen zu können, ist eine kurze Übersicht des LIN-Bus-Protokolls erforderlich. Tiefergehende Informationen bleiben einem späteren Artikel vorbehalten.

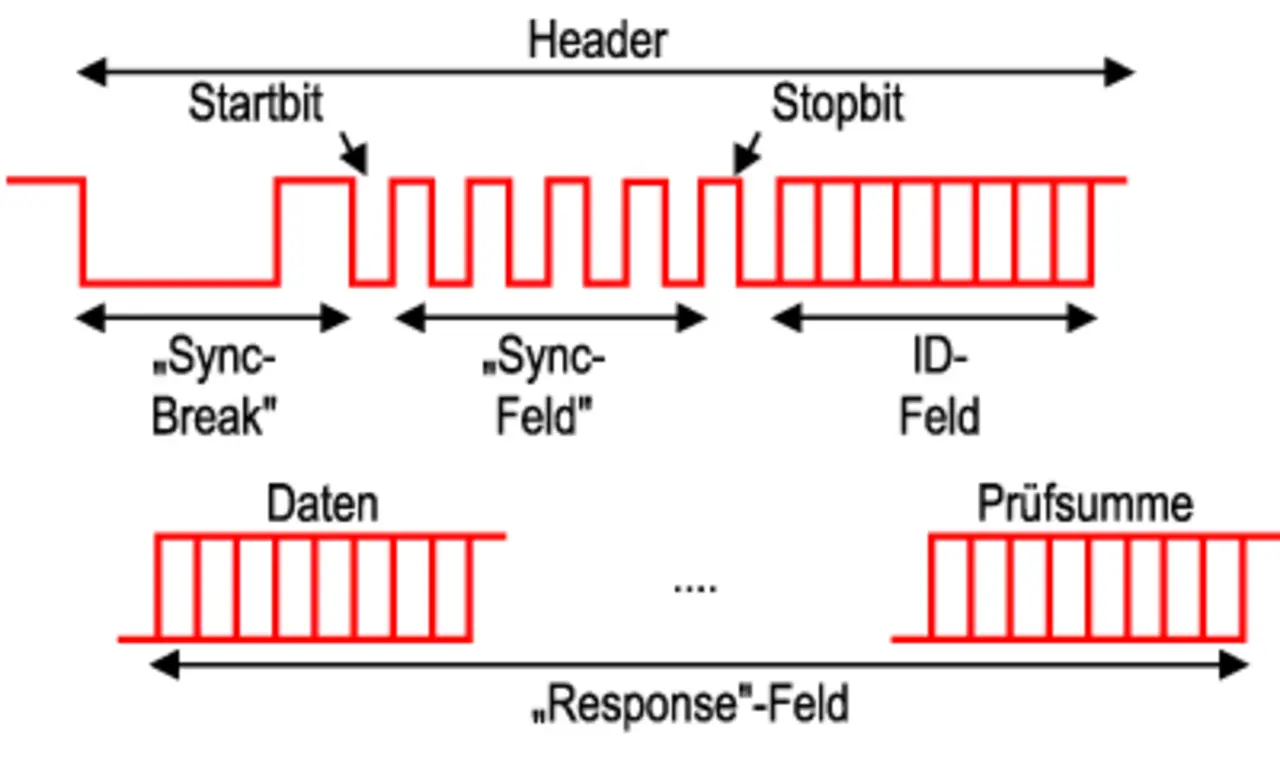

Ein LIN-Bus-Paket besteht aus einem Synchronisationsbreak, einem Synchronisationsfeld, dem ID-Feld und dem Response-Feld mit einer variablen Zahl von Datenbytes, gefolgt von einem Byte mit einer Prüfsumme (Bild 1).

Der Synchronisationsbreak wird durch einen dominanten Zustand des Busses von wenigstens 13 Bitzeiten, gefolgt von einem rezessiven Buspegel für wenigstens eine Bitzeit markiert. Beim LIN-Bus heißt der HIGH-Zustand (= Ubat) rezessiv, der Masse-Pegel (GND) dagegen dominant.

Darauf folgt das Synchronisationsfeld, eingeleitet von einem Startbit (dominant), dem Wert 0x55 und einem Stopbit (rezessiv). Dieses Feld ermöglicht den Slaves die Ermittlung der Übertragungsrate des Masters. Die Anforderungen an die Präzision der Zeitbasis der Slaves sind recht gering: ±15 %, sodass viele Bausteine ohne Quarz arbeiten können.

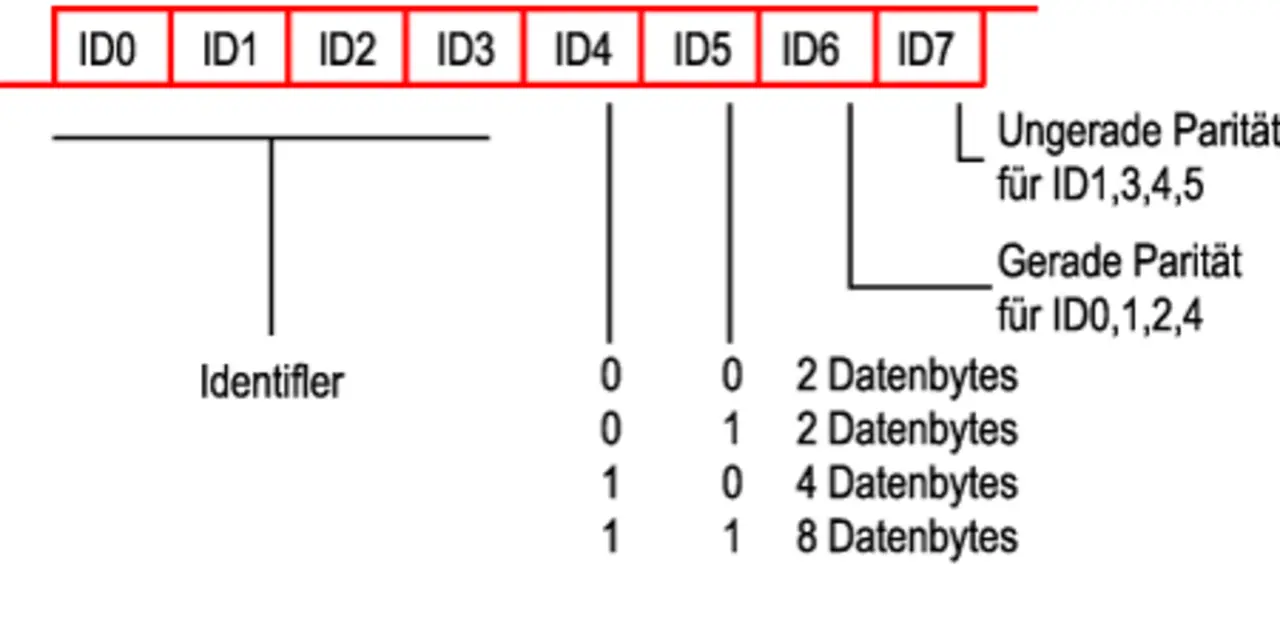

Auch das ID-Feld wird, wie alle Bytefelder, von Start- und Stopbit eingerahmt. Es handelt sich in diesem Bereich also um eine typische asynchrone Kommunikation. Das ID-Feld (Bild 2) enthält neben vier Adressbits ein Längenfeld von 2 bit sowie zwei Parity-Bits. Beim LIN-Bus ist die Adressbelegung nicht fix, sondern die Firmware der Slaves muss wissen, was die einzelnen Codes des ID-Felds bedeuten. Zum Beispiel bedeuten die Längenangaben 00 und 01 im Längenfeld zwar die gleiche Länge des Response-Feldes, die Interpretation des Identifiers ist aber unterschiedlich.

Das Datenfeld variabler Länge, beim LIN-Bus Response-Feld genannt, folgt und wird von einem Prüfbyte gesichert. Die Summe der Datenbytes plus dem Prüfbyte muss 0xff (mod 256) ergeben. Das Response-Feld kann je nach vorangehendem Paket und dem Inhalt des ID-Feldes eine Nachrichtenübertragung vom Master zum Slave oder vom Slave zum Master enthalten.

Weitere Sicherheitsmaßnahmen betreffen die Überwachung der „Bus Idle Time“: Der Bus soll nicht mehr als 25 000 Bitzeiten inaktiv sein zuzüglich der „Slave Response Time“, die von der Übertragungsgeschwindigkeit abhängt.

Bereits diese kurze Beschreibung des LIN-Bus-Protokolls erlaubt die Definition der Aufgaben bei der Abwicklung des Protokolls:

- Erkennung der Sync-Break-Bedingung,

- Synchronisation mit dem Master, d.h. Ermittlung der Baudrate,

- Senden bzw. Empfangen der Datenbytes.

Die CY8C26xxx-Bausteine verfügen neben den zwölf analogen Blöcken, die bereits in [1, 2] beschrieben wurden, zusätzlich über acht digitale Blöcke, die sich ebenfalls wie die analogen Blöcke von der CPU konfigurieren lassen. Ähnlich wie bei den analogen Blöcken haben nicht alle digitalen Blöcke die gleiche Funktion. Es gibt – grob gesagt – zwei Kategorien von digitalen Blöcken: Basisblöcke mit Timer/Zähler-Funktionen und Kommunikationsblöcke, die zusätzlich UART und SPI-Funktionen abwickeln können, und zwar je vier von beiden Kategorien. Alle digitalen Blöcke haben eine Breite von 8 bit, können aber kaskadiert werden, beispielsweise lässt sich mit vier Blöcken ein 32-bit-Timer realisieren.

- Robust und kostengünstig

- Protokollabwicklung in den Slaves