Leiterplattentechnik

Beipässe für große Ströme

Fortsetzung des Artikels von Teil 1

Drähte in der Leiterplatte einbetten

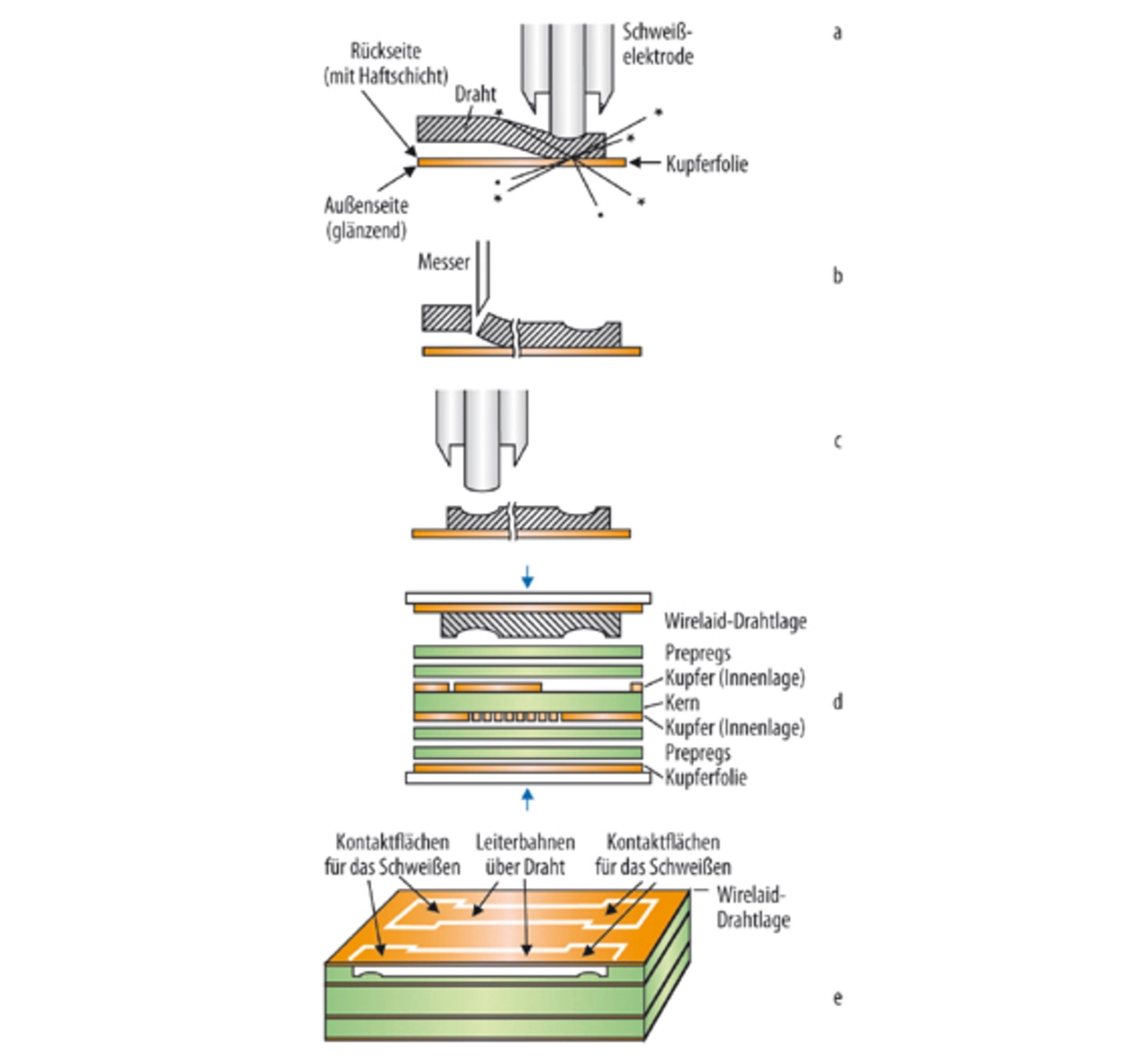

Der Ablauf im Detail:

Die Kupferfolie wird auf dem Vakuumtisch des Automaten fixiert. Über Kennlöcher werden Position und Lage der Folie optisch registriert. Die erste Schweißposition wird angefahren, und über die kontrollierte Z-Achse werden Niederhalter und Schweißelektrode aktiviert. Der Maschinentisch fährt die zweite Schweißposition an. Dabei wird der Draht aktiv nachgeführt und in der Sollposition niedergehalten, geschnitten und verschweißt. Die Gegenelektrode befindet sich dabei stationär unter der Kupferfolie (Bild 2).

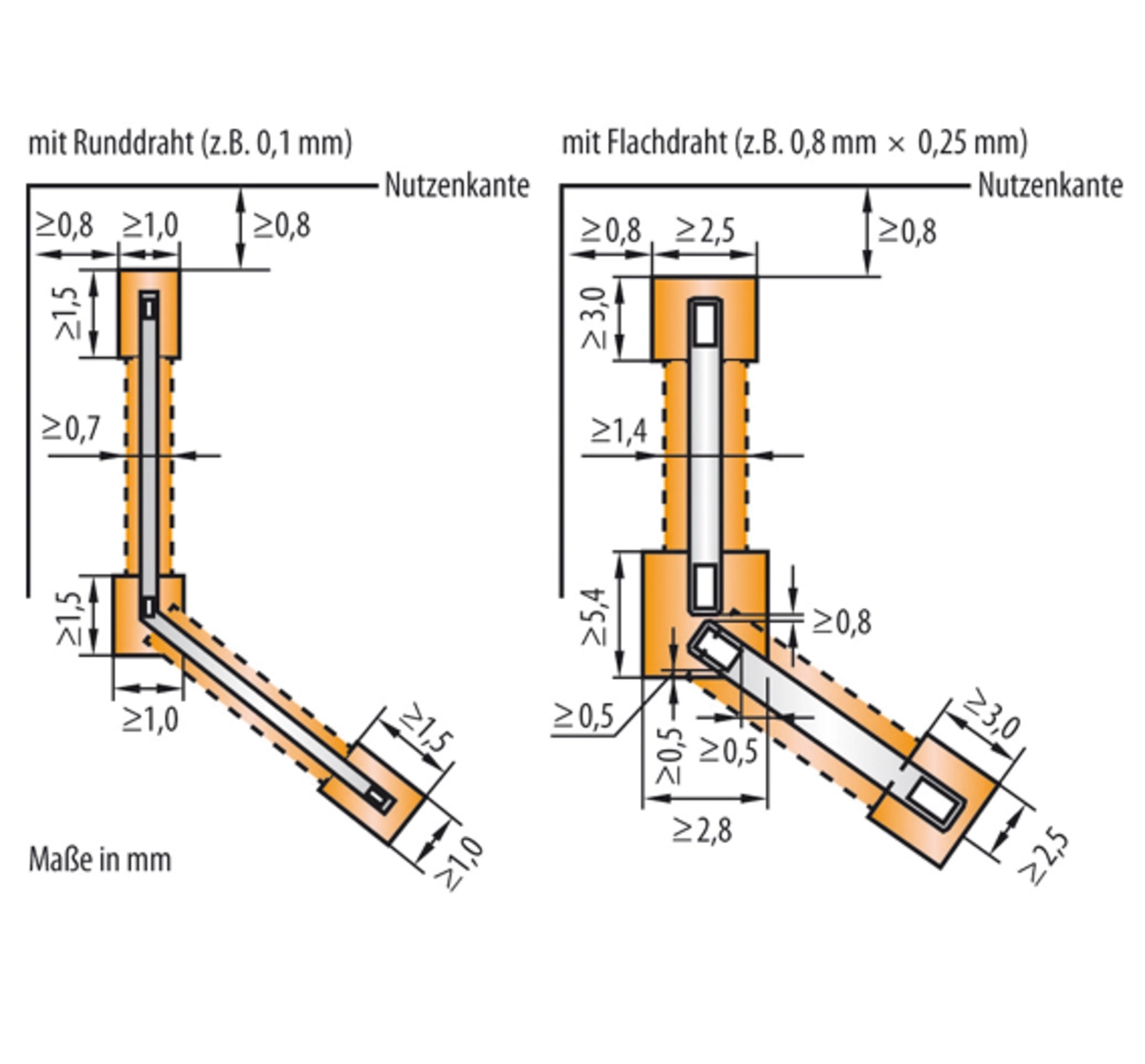

Die frei verlegte Drahtlänge beträgt in Abhängigkeit vom Querschnitt 30 mm bis 100 mm. Bei Längen darüber hinaus sorgen zusätzliche Schweißpunkte für sicheren Halt. Mit Runddrähten können abgewinkelte Leiterführungen in einem Zug mit Stützschweißungen an den Eckpunkten realisiert werden. Flachdrähte werden bis zu den Ecken gezogen, geschnitten und mit der Leiterbahn verschweißt. Dort wird der Flachdraht neu angesetzt, verschweißt und im gewünschten Winkel in der Geraden weiter geführt (Bild 3).

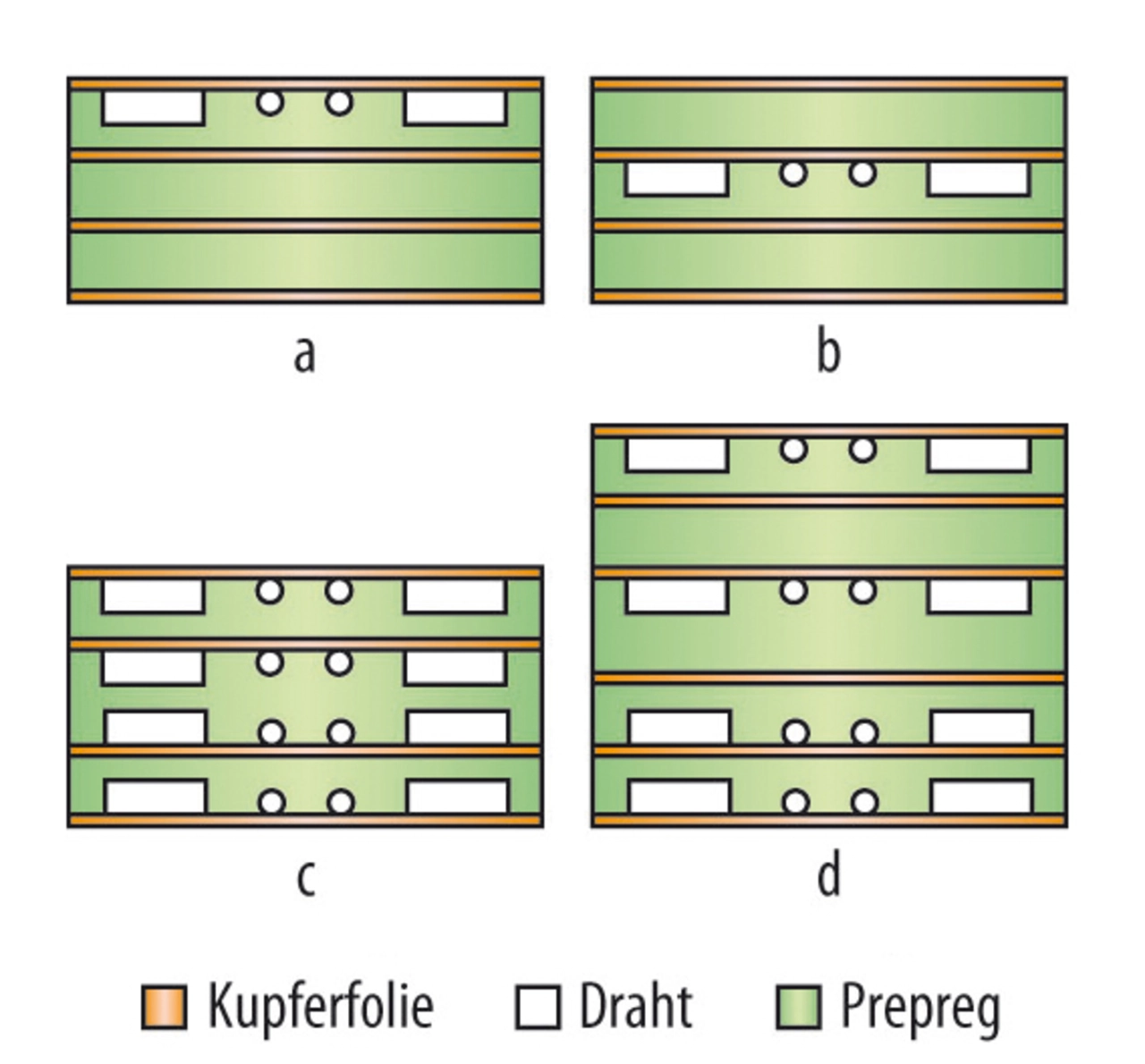

Sind alle Drähte gelegt und an den Enden verschweißt, wird die drahtverstärkte Kupferfolie – Wirelaid-Drahtlage genannt – wie eine normale Kupferfolie weiterverarbeitet und zu einer Leiterplatte verpresst. Wirelaid-Drahtlagen können sowohl für Außenlagen als auch für Innenlagen verwendet werden. Sogar das Stapeln mehrerer Wirelaid-Drahtlagen in einem Multilayer ist möglich (Bild 4). Die Drähte liegen nach dem Verpressen immer im Inneren des Laminates, eingebettet in das Prepreg. Die Außenlagen sind eben und SMT-fähig. Die Stukturierung der Außenlage kann nun entsprechend dem Layout mit Hochstromleiter und Signalverdrahtung auf einer gemeinsamen Ebene vorgenommen werden.

Die eingebetteten Drähte vergrößern den Leitungsquerschnitt ohne zusätzlichem Platzbedarf auf der Oberfläche und ohne dicke Kupferfolien einzusetzen. Mit einem 0,3 mm Runddraht lässt sich z.B eine 0,9 mm breite Leiterbahn aus 35 µm Kupfer auf einen Querschnitt von 0,1 mm2 vergrößern – ausreichend um bis zu 20 A über 10 cm zu transportieren. Ohne angeschweißten 0,3-mm-Draht müsste die Leiterbahn bei gleichem Kupferquerschnitt mindestens 2,9 mm breit sein.

Noch deutlicher fallen die Platzersparnisse bei Flachdraht aus. Der 1,4 mm x 0,35 mm Flachdraht zum Beispiel passt unter eine 2-mm-Leiterbahn und sorgt bei 35 µm Kupfer für eine Stromtragfähigkeit von rund 40 A. Für den gleichen Querschnitt würde eine 16 mm breite Leiterbahn aus 35 µm Kupfer erforderlich sein. Nach IPC müsste unter den gleichen Bedingungen eine Breite von rund 14 mm genügen. Hier kommt die bessere Kühlwirkung der großen Kupferoberfläche zum tragen. Für große Stromstärken – bis zu 100 A – können mehrere Drähte parallel unter eine Leiterbahn geschweißt werden. Für 100 A genügt z.B. eine 10,9 mm breite Leiterbahn aus 70 µm Kupfer mit vier angeschweißen Flachdrähten 1,4 mm x 0,35 m. Nur aus Kuferfolie geätzt müsste die 100-A-Leiterbahn über 24 mm breit sein.

Beim Layout sind Mindestwerte z.B. für die Größe der Kontaktstelle für das Schweißen, die Breite der Leiterbahn über dem Draht, den Abstand zwischen Schweißpunkten und den Abstand zwischen Drähten einzuhalten (Design rules). Die Wirelaid-Drahtlage wird im Layout als eine separate Innenlage geplant und gezeichnet. Sie enthält aber nur die Leiterbahnen, die mit dem Draht verstärkt werden sollen – eine Kopie der Hochstromleiterbahnen von der darüberliegenden Lage. Beim Leiterplattenhersteller werden die Daten der Wirelaid-Lage zum Steuern des Schweißautomaten übersetzt.

Wirelaid statt teuerer Steckverbinder

Wirelaid ermöglicht es auch 3D-Baugruppen zu realisieren, z.B. wenn Semiflexaufbauten oder Leiterplattenverbindungen über Stecker ersetzt werden sollen. Im einfachsten Fall wird ein Teil der Leiterplatte nach dem Bestücken abgewinkelt – z.B. das Anzeige- und Bedienteil – und beim Einbau ins Gehäuse in dieser Position fixiert. Hierzu muss eine Nut in das Basismaterial entlang der gewünschten Biegekante gefräst werden. Das FR4-Substrat wird entlang dieser Nut, deren Frästiefe bis kurz über die Drähte reicht, gebrochen und abgewinkelt. Beim Abwinkeln des Leiterplattensegmentes können die Drähte an der Biegekante teilweise freigelegt werden. Die 2 µm dicke Silberbeschichtung der Drähte bietet hierbei den notwendigen Korrosionsschutz.

Die Drähte, Hochstrom- oder Signalleiter halten die Verbindung zwischen den Segmenten. Diese Lösung erlaubt das bis zu dreimalige Biegen anlässlich der Baugruppenmontage. Der max. Biegewinkel beträgt 105°, der minimale Biegeradius, in Abhängigkeit vom Drahtquerschnitt, 0,1 mm. Dieser minimale Biegeradius, die Hochstromfähigkeit auch im Biegebereich und nicht zuletzt die im Vergleich zu Steckern oder Starrflex Lösungen erheblich niedrigeren Kosten bei gleicher und zum Teil erhöhter Zuverlässigkeit machen die Wirelaid 3D-Technik sehr attraktiv für den Anwender.

Wirelaid-Leiterplatten

Ergänzung der Standard-Leiterplattenfertigung

Die Wirelaid-Technik ergänzt den etablierten Standard-Fertigungsprozess für Leiterplatten. Sie bearbeitet gängige Kupferfolien bevor diese mit Prepegs verpresst werden und bildet somit einen, der klassischen Leiterplattenfertigung vorgelagerten und unabhängigen Prozessschritt. Der etablierte Fertigungsprozess für FR4-Leiterplatten muss für Wirelaid weder verändert noch angepasst werden. Die Qualität der Standard-Leiterplatte kann somit auch auf eine Wirelaid-Leiterplatte übertragen werden.

Elektrische Schweißverbindungen zwischen Kupfer und Kupfer sind seit vielen Jahren bekannt, wurden vielfach untersucht und qualifiziert. In der Wirelaid-Leiterplatte werden diese beiden Prozesse zusammengeführt. Unter anderem hat das Zentrum für Aufbau- und Verbindungstechnik (ZAVT) Wirelaid-Leiterplatten entsprechend einschlägiger Industrienormen geprüft (Tabelle). Dabei kam es zu keinem Ausfall einer Verbindung.

| Test | Norm | Kriterien |

| Hochtemperaturlagerung | Bosch-Norm BV Y273 R80029 | 1000 h bei 140 °C |

| Feuchte-/Klimalagerung | IPC TM-650 | 1000 h bei 85 °C und 85 % RH |

| Temperaturwechseltest | IPC-6012B | 1000 Zyklen -40 °C – +140 °C |

| Bosch-Norm BV Y273 R80029 | 1000 Zyklen -55 °C – +125 °C | |

| Hochspannungsprüfung | an IPC-6012B angelehnt | 60 s: 500 V, Impuls: 5000 V |

| Elektrokorrosion | IPC-6012B / IPC TM-650 | Prüfung auf Silbermigration |

| Schwingfestigkeit (Breitbandrauschen) | DIN EN 60068-2-64 (IEC68-2-6) | Schärfegrad 1 (VW-Norm) |

| Dauerschockprüfung | EN 60068-2-29 | 100000 Impulse (11 ms) mit 50 g |

| Delaminationsprüfung | IPC-6012B | Lötbandtest 10s bei 288 °C |

| Wölbung/Verwindung | IPC TM-650 | < 1% der Diagonale |

| Biegeprüfung Flex-Lötstopplack (bei wirelaid 3D) | IPC-612B | keine Rissbildung im gebogenen Zustand |

| Durchschlagsfestigkeit lateral zwischen Draht und Draht im gebogenen Zustand (bei wirelaid 3D) | IPC-6012B | 60 s: 500 V |

Tabelle. Neben anderen hat das Zentrum für Aufbau und Verbindungstechnik GmbH (ZAVT) in Lippstadt Wirelaid-Leiterplatten entsprechend industrieüblicher Normen geprüft. Alle Tests wurden ohne Beanstandung bestanden. (Quelle: Jumatech GmbH)

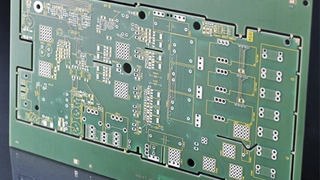

Wirelaid-Leiterplatten sind so zuverlässig wie Leiterplatten und erlauben es Leistungs- und Steuerelektronik auf einer gemeinsamen Leiterplatte zu platzieren. Wirelaid-Leiterplatten werden in Deutschland von mehreren namhaften Leiterplattenherstellern gefertigt — in Serienstückzahlen ebenso wie als Express-Prototypen. Japanische Leiterplattenhersteller bereiten die Produktion von Wirelaid-Leiterplatten für das nächste Jahr vor. Die Wirelaid-Technik ist auf dem Weg, sich international als eine Standardtechnik für Hochstrom-Leiterplatten zu etablieren.

Der Autor:

| Jürgen Westenkirchner |

|---|

| Jahrgang 1965, ist seit 2004 bei bei der Jumatech GmbH tätig. Er betreut technische Schnittstelle zwischen dem Kunden und der Fertigung die Umsetzung der Wirelaid-Technik. Herr Westerkirchner startete mit einer Ausbildung zum Funkelektroniker und arbeitete anschließend im Messgerätebau der Grundig AG. Nach dem Studium der Nachrichtentechnik an der Fachhochschule Nürnberg folgten Tätigkeiten in der Entwicklung von Werkzeugmaschinensteuerungen sowie der Entwicklung von DSP/FPGA-basierten Hochgeschindigkeitskameras, jeweils einschließlich des Layoutes der entsprechenden Leiterplatten. |

Juergen.westenkirchner@jumatech.com

- Beipässe für große Ströme

- Drähte in der Leiterplatte einbetten